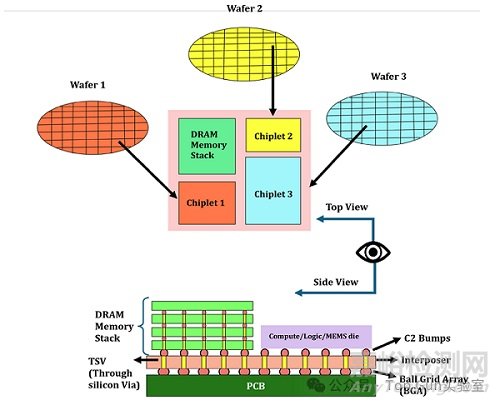

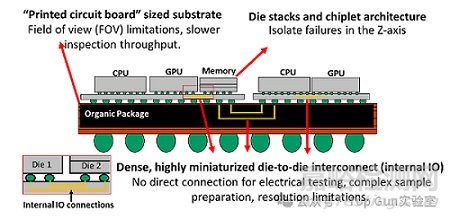

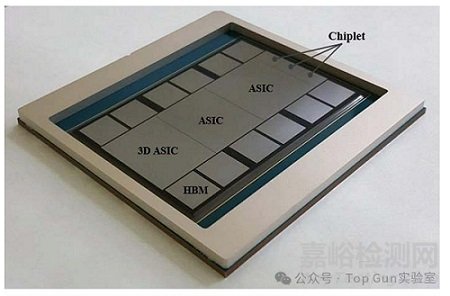

先進封裝技術(shù)通過密集的芯片間互連(D2D)�、2.5D中介層、3D芯片堆疊以及在中介層上的3.5D芯片堆疊,實現(xiàn)了芯粒(Chiplet)的異質(zhì)集成。這些創(chuàng)新正以更低的成本延續(xù)摩爾定律,因為通過光刻技術(shù)進行晶體管縮微的傳統(tǒng)方法已變得越來越昂貴��。通過利用具有更小芯片尺寸的優(yōu)化芯粒�����,異質(zhì)集成提升了器件性能�����、降低了成本并提高了良率�����。然而��,這也給IC封裝帶來了重大挑戰(zhàn)。

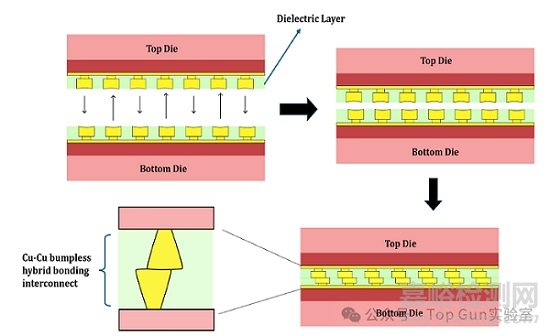

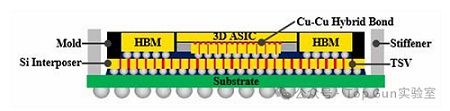

隨著互連節(jié)距縮小至10μm以下甚至1μm���,晶圓上芯片(DoW)和晶圓上晶圓(WoW)混合銅鍵合(HCB)技術(shù)正在取代基于焊料的微凸塊熱壓鍵合(TCB)用于芯片堆疊�����。雖然互連變得更小�����、更密集��,但為了滿足高性能計算(HPC)和人工智能(AI)應(yīng)用不斷增長的需求�����,集成了更多芯粒和高帶寬內(nèi)存(HBM)���,整體封裝尺寸卻在增大���。這些市場要求更高的性能�����、更低的功耗�����、更寬的內(nèi)存帶寬和更低的延遲。

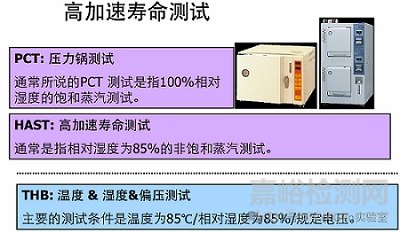

為確保復(fù)雜先進封裝的可靠性�����,需進行各種標(biāo)準(zhǔn)可靠性測試以加速模擬真實使用條件�����。標(biāo)準(zhǔn)可靠性測試包括以下內(nèi)容:

預(yù)處理(PC)測試:涉及濕熱浸泡和多次回流�����,以模擬運輸���、存儲和印刷電路板(PCB)組裝條件。

溫度循環(huán)(TC)測試:使器件經(jīng)受極端溫度波動�����,以模擬反復(fù)的通電/斷電循環(huán)。

烘烤測試:將器件暴露于長時間高溫下��,以模擬長期運行��。

無偏置高加速應(yīng)力測試(UHAST)和有偏置高加速應(yīng)力測試(BHAST):模擬高溫高濕的惡劣環(huán)境���,其中BHAST還施加電偏置。

每次可靠性測試都會誘發(fā)特定的失效模式和機制�����。例如��,PC測試可能因回流過程中吸收的水分或有機污染物產(chǎn)生的蒸汽壓而導(dǎo)致爆米花效應(yīng)或分層���。TC測試通常導(dǎo)致與熱機械應(yīng)力相關(guān)的失效�����,如焊點疲勞或基板走線開裂��。烘烤測試可能導(dǎo)致金屬間化合物(IMC)老化或材料退化��。UHAST失效通常與腐蝕相關(guān)���,而BHAST失效則因施加的偏置同時涉及腐蝕和電化學(xué)反應(yīng)��。

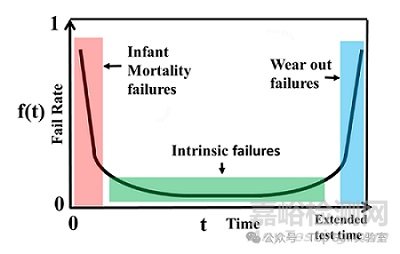

理解可靠性測試中的失效率分布對于識別失效是缺陷驅(qū)動�����、本質(zhì)失效還是由于損耗至關(guān)重要���。著名的“浴盆曲線”說明了三個失效階段:

早期失效(Infant Mortality Failures):源于工藝缺陷,可通過優(yōu)化組裝工藝或?qū)嵤┖Y選測試來緩解�����。

本質(zhì)失效(Intrinsic Failures):以恒定速率發(fā)生���,源于設(shè)計���、部件選擇或應(yīng)用特定因素,通常需要重大的工藝改進來緩解���。

損耗失效(Wear-Out Failures):在長時間測試后出現(xiàn)��,標(biāo)志著器件壽命的終結(jié)�����。

故障隔離(Fault Isolation��,F(xiàn)I)和失效分析(Failure Analysis��,F(xiàn)A)技術(shù)對于在可靠性測試后或在生產(chǎn)線終端(EOL)識別導(dǎo)致電氣失效的缺陷至關(guān)重要���。一旦缺陷被定位,F(xiàn)A方法便被用來調(diào)查其根本原因���、提出失效機制并為解決問題提供反饋�����。FA在封裝技術(shù)發(fā)展中扮演著關(guān)鍵角色���。然而,隨著封裝尺寸增大和設(shè)計日益復(fù)雜��,F(xiàn)A面臨著巨大的挑戰(zhàn)�����。

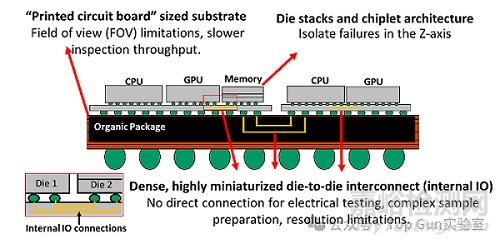

在高帶寬內(nèi)存(HBM)等堆疊芯片結(jié)構(gòu)中,獲取有關(guān)缺陷的Z軸信息至關(guān)重要�����。此外��,當(dāng)封裝尺寸超過100 mm x 100 mm時���,由于大多數(shù)FA工具的視場(FOV)限制���,對整個封裝進行檢測變得困難。雖然可以采用圖像拼接技術(shù)�����,但這會降低檢測吞吐時間(TPT)���。再者��,可靠性測試后單個封裝內(nèi)可能存在多個電氣失效��,使得在三維(x, y, z)空間中進行非破壞性失效定位成為一大挑戰(zhàn)�����。另一個關(guān)鍵問題是密集的芯片間(D2D)互連的故障隔離��,這些互連通常缺乏直接的焊球陣列(BGA)接入點進行電氣測試��,在復(fù)雜的樣品制備和有限的FI-FA工具分辨率方面面臨重大挑戰(zhàn)���。

除了電氣FA挑戰(zhàn)之外��,挑戰(zhàn)還延伸至成像、物理FA和材料分析領(lǐng)域�����。迫切需要具有高分辨率和大視場的非破壞性成像技術(shù)���。在大面積區(qū)域內(nèi)進行樣品制備以揭示細(xì)微缺陷且無偽影的技術(shù)是物理FA的關(guān)鍵挑戰(zhàn)�����。在界面處檢測百萬分之一(ppm)級別的污染���,以及以亞微米分辨率識別有機污染是材料分析領(lǐng)域的主要挑戰(zhàn)。

從商業(yè)角度來看�����,為滿足行業(yè)對更短產(chǎn)品開發(fā)周期、大批量制造和成本效益的需求��,先進封裝的FI-FA需要優(yōu)先考慮:

低成本��。

快速周轉(zhuǎn)��。

高缺陷檢測成功率��。

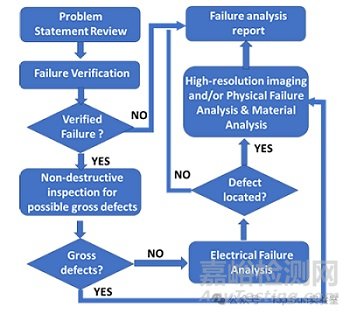

一個結(jié)構(gòu)良好的FI-FA工作流程對于在合理時間內(nèi)識別復(fù)雜封裝中的電氣失效至關(guān)重要���。典型的FI-FA流程包括:

問題陳述評審���。

失效驗證。

非破壞性成像調(diào)查���。

電氣失效分析��。

物理失效分析���。

材料分析。

盡管常被工程師低估��,但問題陳述評審實際上是FA中非常關(guān)鍵的一步。它涉及收集關(guān)鍵信息���,包括:

失效發(fā)生條件和歷史:了解失效是發(fā)生在EOL��、可靠性測試期間還是客戶退貨��。EOL失效通常表明工藝相關(guān)缺陷���,而可靠性失效則是極端應(yīng)力條件的結(jié)果?��?蛻敉素浭枰獊碜袁F(xiàn)場的詳細(xì)熱歷史和測試歷史�����。

失效率分析:高EOL失效率表明存在重大工藝問題,而低失效率可能意味著隨機缺陷���?�?煽啃允ё裱?ldquo;浴盆曲線”�����,失效模式分為早期失效��、本質(zhì)失效或損耗失效���,每種情況需要不同的FA方法��。

利用歷史FA數(shù)據(jù):來自類似系統(tǒng)的過往失效案例可以指導(dǎo)FA策略���,有時甚至無需進行廣泛的電氣和物理分析即可識別缺陷。

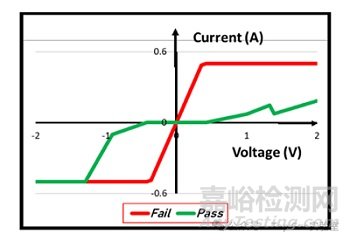

在進行耗時的FA步驟之前�����,需要進行失效驗證以排除測試儀接觸問題��、測試程序不成熟和間歇性失效��。對于開路和短路等參數(shù)失效��,需將電流-電壓(I-V)曲線和電阻測量值與良品(Passing)器件進行比較�����。功能失效則使用調(diào)試測試儀和測試程序進行驗證,以確認(rèn)其與通過單元的偏差���。

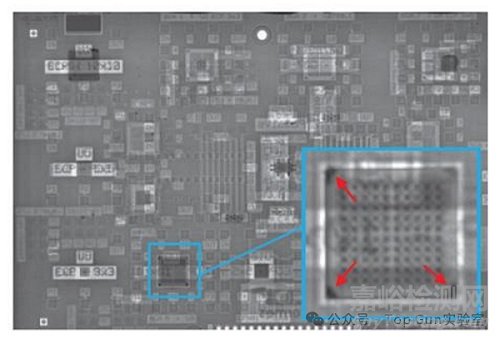

一旦失效得到驗證���,便使用具有大視場的非破壞性成像技術(shù)檢查整個AOI��。例如���,可以使用光學(xué)顯微鏡檢查整個封裝���,尋找任何可能的操作損傷。掃描聲學(xué)顯微鏡(SAM)可用于掃描包括所有芯片在內(nèi)的整個封裝�����,以檢查大的分層或裂紋��。如下圖所示顯示了一個帶嵌入式芯片的PCB的穿透式SAM(TSAM)掃描圖��。紅色箭頭指向一個嵌入式芯片芯片角落的“暗點”�����,表明存在芯片裂紋���。

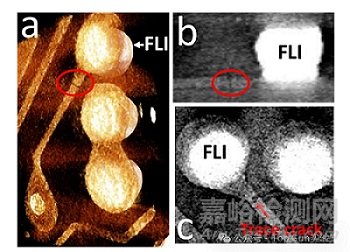

通過優(yōu)化傾斜和旋轉(zhuǎn)角度���,可使用2D X射線實時檢查整個凸塊區(qū)域的焊點完整性并識別有缺陷的焊點。如下圖所示�����,先進封裝中一級互連FLI(即芯片與有機基板之間的焊點)的2D X射線圖像���。這些2D X射線圖像是在沒有任何樣品制備的情況下非破壞性拍攝的��。通過識別在優(yōu)化樣品傾斜和旋轉(zhuǎn)條件下拍攝的2D X射線圖像中的不同幾何形狀,可以識別FLI缺陷,如非接觸開路�����、未潤濕和部分未潤濕�����,這將大大提高FA的TPT。

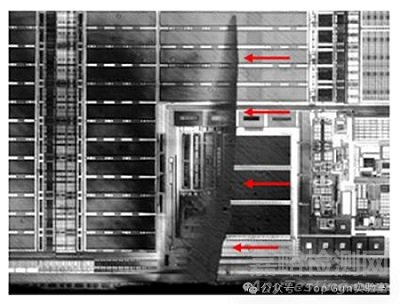

紅外顯微鏡成像可用于檢查所有芯片是否存在內(nèi)部裂紋�����。如下圖所示,展示了一張從未經(jīng)任何樣品制備(如芯片減薄)的先進封裝芯片背面拍攝的紅外圖像��。圖像中紅色箭頭指向的暗影表明存在內(nèi)部芯片裂紋�����,該裂紋已擴展到芯片有源區(qū)并損壞了電路�����,導(dǎo)致電氣失效���。

如果非破壞性成像揭示了明顯的缺陷�����,則該單元將繞過電氣故障隔離�����,直接進入物理和材料分析。然而,如果未發(fā)現(xiàn)明顯缺陷,則需要進行詳細(xì)的電氣FA。

電氣FA可以在非常復(fù)雜的先進封裝中精確定位細(xì)微缺陷�����。在封裝級別無需樣品制備的常用技術(shù)包括:時域反射計(TDR)�����、電光太赫茲脈沖反射計(EOTPR)��、鎖定熱成像(LIT)和磁場成像(MFI)��。光學(xué)故障隔離工具��、電子束成像和探針技術(shù)通常用于器件功能失效的FA,這需要芯片減薄和分層。在復(fù)雜的樣品制備后進行微米或納米尺度的探針測試對于定位失效也非常有效��。通常結(jié)合使用各種類型的故障隔離工具來定位先進封裝中的失效點。

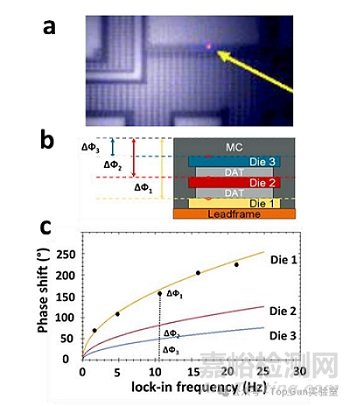

非破壞性��、高分辨率的故障隔離(FI)技術(shù)能夠在三維(x, y, z)空間中識別缺陷�����,這對于先進封裝失效分析(FA)至關(guān)重要,特別是對于存在多個失效點的單元��。鎖定熱成像(LIT)在檢測三維空間中的短路和阻性失效方面尤其有效�����,且無需樣品制備���。LIT通過利用熱傳播的時間依賴性特性提供Z軸缺陷定位。激勵信號與由此產(chǎn)生的熱響應(yīng)之間的相位偏移與熱擴散相關(guān)的時間延遲相對應(yīng)���。該相位偏移受激勵信號的鎖頻、以及器件各層的熱特性和厚度的影響���。通過將來自已知缺陷深度的參考單元的鎖頻與相位偏移曲線進行比較�����,可以確定器件內(nèi)熱點(hotspot)的Z位置�����。如下圖(a-c)所示�����,展示了實驗和模擬的LIT數(shù)據(jù)���,證明了其區(qū)分堆疊芯片內(nèi)不同位置熱點的能力���。結(jié)果證實LIT能有效揭示所有三個維度上的缺陷位置。然而��,雖然LIT擅長精確定位泄漏和高阻失效(3D)��,但它不適用于隔離硬開路或電阻低于1歐姆的短路失效��。在這種情況下��,應(yīng)使用磁場成像(MFI)��、時域反射計(TDR)和電光太赫茲脈沖反射計(EOTPR)等替代技術(shù)�����。

對于內(nèi)部IO失效分析��,如下圖所示���,由于內(nèi)部芯片間互連缺乏焊球陣列(BGA)連接�����,故障隔離面臨挑戰(zhàn)�����。為了解決這個問題�����,需要在產(chǎn)品測試程序開發(fā)階段開發(fā)專門的故障隔離測試程序���,以精確定位失效源:是來自芯片1��、芯片2,還是它們之間的互連���。如果失效追溯到芯片間的互連���,則可以將樣品制備技術(shù)與3D微探針技術(shù)結(jié)合使用,配合FI工具(如時域反射計(TDR)��、電光太赫茲脈沖反射計(EOTPR)或鎖定熱成像(LIT))來識別內(nèi)部IO連接中的缺陷。

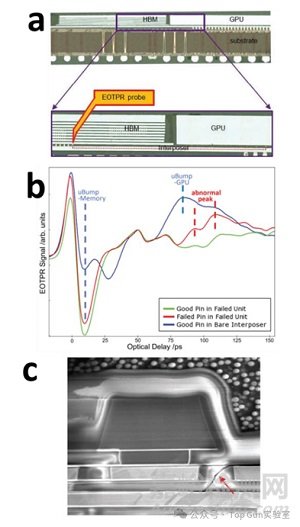

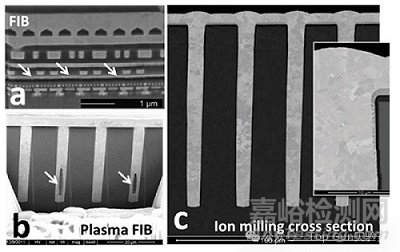

如下圖所示��,對失效單元進行了精密的截面制備���,以暴露部分連接到有缺陷的內(nèi)部IO引腳的微凸塊�����,該引腳位于高帶寬內(nèi)存(HBM)和硅中介層之間�����。使用微探針技術(shù)���,將EOTPR探針施加到部分暴露的微凸塊上,然后收集EOTPR數(shù)據(jù)�����,如(b)所示��。通過將獲取的頻譜與已知良品引腳和裸中介層的頻譜進行比較���,將失效定位到GPU芯片上���,靠近連接GPU和硅中介層的微凸塊處���。為了進一步研究,進行了等離子體聚焦離子束(FIB)截面分析���,揭示了缺陷��。如(c)顯示了一張掃描電子顯微鏡(SEM)圖像��,顯示了一層介質(zhì)層(ILD)裂紋���,該裂紋有可能擴展為內(nèi)部IO引腳布線中的通孔分層或走線裂紋。

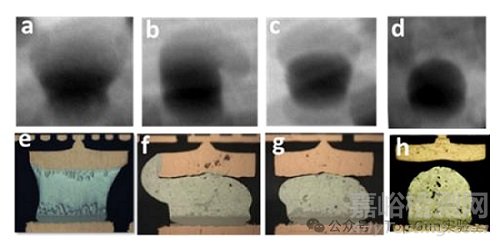

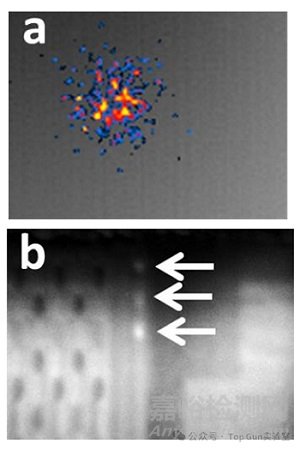

在故障隔離之后���,強烈建議在進行詳細(xì)的物理失效分析(PFA)之前再進行一輪高分辨率�����、非破壞性(對AOI)的成像。根據(jù)缺陷的尺寸���、類型和所用成像技術(shù)的分辨率���,可能無需進行PFA即可識別缺陷��。如下圖所示���,使用鎖定熱成像(LIT)精確定位了失效位置,在(a)中顯示為一個“熱點”�����。相位偏移角分析進一步表明該缺陷位于堆疊芯片封裝的上層芯片中�����。為了更仔細(xì)地檢查該區(qū)域���,在“熱點”區(qū)域周圍使用了高分辨率C模式掃描聲學(xué)顯微鏡(CSAM)進行局部掃描���。如(b)所示,CSAM檢測到了“白色凸點”���,表明存在層間介質(zhì)(ILD)分層��。這類缺陷會發(fā)展成芯片內(nèi)的通孔或走線開路��,最終導(dǎo)致高阻失效��。

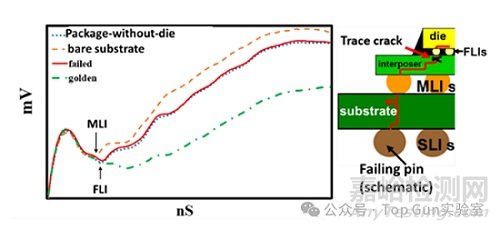

如下圖所示���,展示了從一個具有2.5D中介層配置的失效單元的失效引腳捕獲的時域反射計(TDR)頻譜�����。通過將該頻譜與良品單元��、裸基板和沒有芯片的良品單元的頻譜進行比較�����,將開路失效精確定位在連接芯片與中介層的一級互連(FLI)焊點附近���。

為了進一步研究該缺陷,使用了高分辨率3D X射線計算機斷層掃描(CT)���,揭示了緊鄰FLI之前的一條走線裂紋��,如下圖所示�����。

物理失效分析(PFA)和材料分析在揭示缺陷細(xì)節(jié)和識別失效根本原因方面起著關(guān)鍵作用���。所選擇的PFA技術(shù)需要在保證相對較短的吞吐時間(TPT)的同時,通過最大限度地減少偽影來保持感興趣區(qū)域(AOI)的完整性��。對于有機PCB�����、基板或大型焊點中的明顯缺陷�����,機械截面或平面研磨是首選��,因為它成本較低且TPT更快��。然而�����,為了檢測有機基板�����、微米級互連和芯片層中的細(xì)微缺陷,通常需要結(jié)合使用機械方法�����、激光燒蝕或銑削�����、離子銑削和FIB等技術(shù)�����,以在較短的TPT內(nèi)實現(xiàn)無偽影的結(jié)果��。

如下圖所示���,一個FIB截面揭示了芯片級別的層間介質(zhì)(ILD)分層�����。為了加速在較大結(jié)構(gòu)中暴露細(xì)微缺陷的過程���,可使用等離子體FIB或離子銑削進行更快的材料去除。圖(b)和(c)分別展示了使用等離子體FIB和離子銑削獲得的硅通孔(TSV)的截面掃描電子顯微鏡(SEM)圖像。

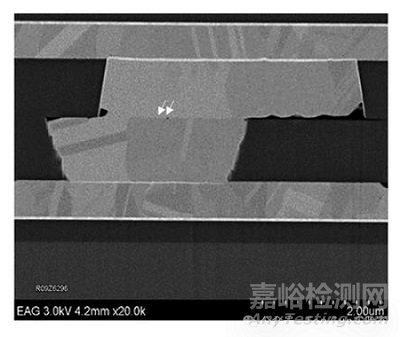

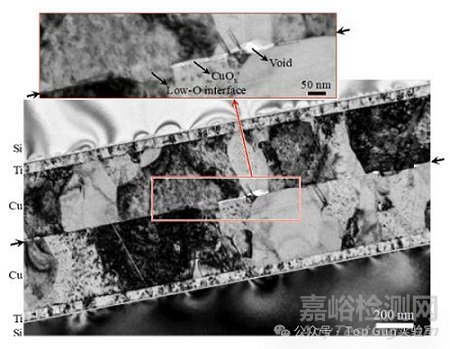

在PFA過程中識別出缺陷后��,會使用各種成像技術(shù)進行詳細(xì)檢查��。光學(xué)顯微鏡通常用于明顯的缺陷成像���,而SEM則常用于亞微米缺陷分析。然而�����,隨著互連尺寸縮小至僅幾微米�����,SEM單獨觀察細(xì)微的界面缺陷(如納米尺度的空洞或分層)可能不夠清晰��。為了實現(xiàn)原子級空間分辨率���,可使用透射電子顯微鏡(TEM)來檢測這些精細(xì)尺度的缺陷��。如下圖所示���,展示了一個混合鍵合Cu-Cu互連的截面SEM圖像,其中界面的細(xì)微缺陷難以清晰辨別。

相比之下��,下圖中的TEM圖像提供了高度詳細(xì)的視圖���,清晰地顯示了Cu-Cu界面處的納米尺寸空洞���。

對缺陷進行全面的材料分析對于深入的根源調(diào)查至關(guān)重要,有助于在先進封裝開發(fā)中確定解決路徑�����。結(jié)合使用材料分析技術(shù)�����,包括能量色散X射線光譜(EDX)�����、傅里葉變換紅外光譜(FTIR)��、基于原子力顯微鏡的紅外光譜(AFM-IR)�����、光學(xué)光熱紅外顯微光譜(O-PTIR)、X射線光電子能譜(XPS)��、飛行時間二次離子質(zhì)譜(TOF-SIMS)和電子背散射衍射(EBSD)��,可以提供關(guān)于感興趣區(qū)域元素組成��、光譜指紋���、化學(xué)狀態(tài)、深度剖析和晶體取向的關(guān)鍵信息�����。

失效分析報告是整個流程的最后一步���,記錄了問題陳述���、分析步驟、結(jié)果和結(jié)論���。詳細(xì)的報告對于在根源調(diào)查期間與合作伙伴進行有效溝通至關(guān)重要��,也是未來案例的寶貴參考��。

先進3D封裝中的高度功能集成和復(fù)雜封裝架構(gòu)給傳統(tǒng)的故障隔離(FI)和失效分析(FA)方法帶來了重大挑戰(zhàn)��。此外�����,大批量制造要求創(chuàng)新的FA工作流程�����,以縮短吞吐時間(TPT)���。將AI集成到FA流程中可以增強自動化和大數(shù)據(jù)分析能力�����,從而降低人工成本��、縮短TPT��,并提高分析復(fù)雜微電子器件的可擴展性��。

近年來�����,半導(dǎo)體行業(yè)越來越多地在FA流程中采用AI���,在以下幾個領(lǐng)域取得了顯著成果:

缺陷檢測和分類���。

在SEM、TEM��、SAM和X射線成像中的降噪��。

通過聚類和模式識別進行失效模式識別��。

FA數(shù)據(jù)和報告分類�����,以及失效模式預(yù)測��。

未來AI在FA中的應(yīng)用可能包括:

輔助跨不同工具的數(shù)據(jù)收集或完全自主執(zhí)行FA��。

培訓(xùn)新FA工程師使用FI-FA工具���。為各種樣品生成或修改針對罕見失效模式的測量數(shù)據(jù)。

自動化生成和評估FA報告�����。

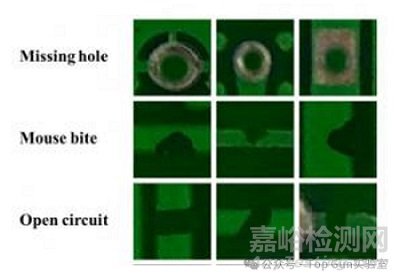

如下圖所示,光學(xué)顯微鏡用于自動捕獲PCB圖像并分析其是否存在缺陷���。訓(xùn)練一個卷積神經(jīng)網(wǎng)絡(luò)(CNN)來自動檢測和分類諸如missing hole���、mouse bite 和 open circuit等缺陷,無需人工干預(yù)��。該機器學(xué)習(xí)模型可以擴展以適應(yīng)更多的缺陷類型和PCB尺寸�����。類似的AI驅(qū)動方法已在全行業(yè)實施��,用于通過光學(xué)顯微鏡���、紅外(IR)顯微鏡���、SAM、X射線��、SEM和TEM實現(xiàn)自動缺陷檢測和分類���。

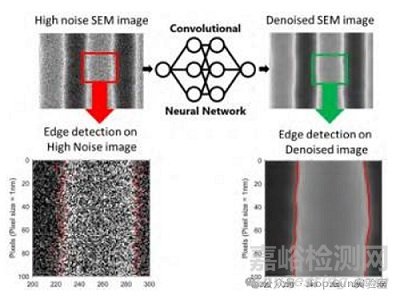

下圖展示了利用AI對SEM圖像進行降噪的應(yīng)用��。訓(xùn)練一個CNN來有效降低SEM圖像噪聲�����,增強圖案邊緣檢測�����。該技術(shù)也可應(yīng)用于對光學(xué)��、IR���、TEM�����、SAM和X射線成像獲得的圖像進行降噪。

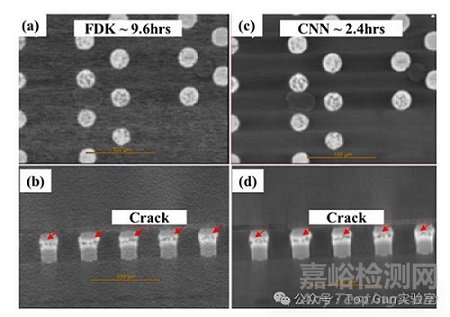

下圖比較了使用傳統(tǒng)的Feldkamp-Davis-Kress(FDK)重建方法與基于CNN的重建方法對微凸塊互連缺陷進行3D X射線計算機斷層掃描(CT)的圖像質(zhì)量�����。圖(a-b)所示的FDK方法需要1600次投影和9.6小時的掃描才能解析一個約1μm厚的凸塊裂紋���。相比之下�����,圖(c-d)所示的基于CNN的重建僅使用400次投影和顯著縮短的2.4小時掃描���,就實現(xiàn)了具有可比性且噪聲更低的圖像質(zhì)量���。這些結(jié)果突顯了基于深度學(xué)習(xí)的重建算法在提高掃描效率同時不犧牲圖像質(zhì)量方面的優(yōu)勢。

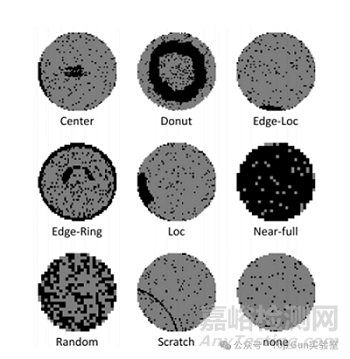

如下圖所示�����,AI已被證明可以提高失效模式識別的效率��。圓圈代表晶圓��,深色點標(biāo)記了失效芯片的位置�����。識別晶圓失效模式對于調(diào)查失效模式和機制至關(guān)重要��。例如,“center””�����、“donut”和“edge”等模式通常指向特定的晶圓級工藝問題���,而“scratch”模式則通常表明操作問題���。通過聚類和模式識別的AI輔助失效模式識別可廣泛應(yīng)用于產(chǎn)品良率分析、制造缺陷監(jiān)控��、器件失效分析和失效根源調(diào)查等領(lǐng)域��。

實現(xiàn)芯粒(Chiplet)異質(zhì)集成的先進封裝技術(shù)���,正在推動半導(dǎo)體行業(yè)持續(xù)前進�����。封裝日益增長的復(fù)雜性和尺寸���,對質(zhì)量保證���、可靠性風(fēng)險評估以及故障隔離與失效分析(FI-FA)技術(shù)提出了嚴(yán)峻挑戰(zhàn)���。為應(yīng)對挑戰(zhàn)�����,F(xiàn)I-FA技術(shù)未來發(fā)展需聚焦以下方向:

AI應(yīng)用:深化人工智能在缺陷檢測���、降噪、模式識別和自動化分析中的應(yīng)用��。

快速��、高分辨率���、非破壞性故障隔離與成像技術(shù):開發(fā)能夠滿足大型�����、復(fù)雜封裝三維分析需求的工具��。

面向具背面供電網(wǎng)絡(luò)(BSPDN)先進封裝的FI-FA方法:BSPDN將在未來先進硅節(jié)點中實現(xiàn)���,需開發(fā)針對性分析手段。

具有亞微米分辨率且樣品制備要求最低或無要求的靈敏材料分析工具:提升對界面污染和微小缺陷的表征能力。

建模與仿真輔助的FA:通過模擬高效定位潛在失效位置���。

面向測試和FA的設(shè)計(DFT/DFA):在產(chǎn)品設(shè)計階段即納入便于FI-FA的測試程序�����。

本文全面綜述了先進封裝技術(shù)(包括2.5D和3D封裝)中故障隔離(FI)與失效分析(FA)技術(shù)所面臨的挑戰(zhàn)�����。詳細(xì)闡述了在芯片級和封裝級故障隔離��、高分辨率成像���、芯片移除、分層���、截面分析���、微探針測試、電子顯微鏡及材料分析中使用的FI-FA技術(shù)�����。此外,還重點介紹了人工智能(AI)輔助的FI和FA方法當(dāng)前的能力和未來發(fā)展趨勢���。