想象一下��,芯片內(nèi)部有一個(gè)隱秘的“自殺開關(guān)”���。一旦被意外觸發(fā)�����,它就會(huì)強(qiáng)制芯片內(nèi)部形成一條低阻通路���,相當(dāng)于在電源(VDD)和地(GND)之間直接“短路”�����。巨大的電流將洶涌流過這條通路�,遠(yuǎn)遠(yuǎn)超過芯片設(shè)計(jì)所能承受的負(fù)載��。這就是閂鎖效應(yīng)(Latch-up)���,一旦啟動(dòng),就會(huì)造成:

- 電流激增: 流經(jīng)芯片的電流瞬間飆升����。

- 電壓崩潰:芯片的電源電壓因巨大電流被拉低。

- 功能癱瘓:芯片完全失去正常工作能力����。

- 熱失控:巨大電流產(chǎn)生的熱量可能導(dǎo)致芯片內(nèi)部局部甚至整體熔化燒毀。

本質(zhì):閂鎖效應(yīng)是CMOS結(jié)構(gòu)內(nèi)部寄生可控硅(Parasitic Silicon Controlled Rectifier, SCR)被意外觸發(fā)導(dǎo)通的結(jié)果��。這是CMOS工藝(將NMOS和PMOS晶體管做在同一芯片上)天生的結(jié)構(gòu)所帶來的不可避免的“副作用”�。

二、閂鎖效應(yīng)的失效機(jī)理

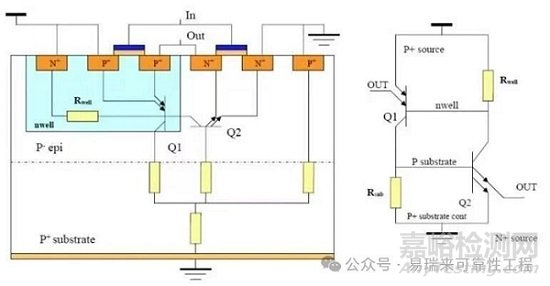

讓我們從CMOS器件的微觀層面深入理解這個(gè)“幽靈開關(guān)”����。在一個(gè)典型的CMOS反相器結(jié)構(gòu)旁邊,存在著由寄生晶體管和寄生電阻構(gòu)成的隱藏結(jié)構(gòu)�,它們共同組成了一個(gè)

寄生的可控硅器件(SCR)

寄生四層結(jié)構(gòu)(PNPN):CMOS工藝在硅襯底上形成N阱(N-well)和P襯底(P-substrate)。這自然地形成了一個(gè)由P+源漏區(qū)(在N-well中)�、N-well、P-substrate�����、N+源漏區(qū)(在P-substrate中)串聯(lián)而成的PNPN四層結(jié)構(gòu)(如下圖)。這正是SCR的典型結(jié)構(gòu)����。

寄生雙極管:在這個(gè)PNPN結(jié)構(gòu)中,隱含了兩個(gè)雙極晶體管:縱向PNP管 (Q1)��; 橫向NPN管 (Q2)

寄生電阻:N-well本身具有一定的電阻(Rnwell)�,P-substrate本身也具有一定的電阻(Rpsub)

觸發(fā)過程:

1)干擾出現(xiàn):一個(gè)來自外部的“刺激”(干擾)出現(xiàn)。例如:

• 輸入端或輸出端受到一個(gè)超出電源軌的電壓過沖(EOS)或靜電放電(ESD)����。

• 電源電壓發(fā)生快速瞬變(dI/dt或dU/dt過大)。

• 芯片暴露在輻射環(huán)境(如宇宙射線)下產(chǎn)生大量載流子。

• 高溫環(huán)境降低寄生晶體管的開啟閾值。

2)基極啟動(dòng):這個(gè)干擾(如注入電流)使得Q1或Q2的基極-發(fā)射極結(jié)被正向偏置���,或者直接注入足夠的少數(shù)載流子進(jìn)入基區(qū)(襯底或N阱)�。

3)正反饋形成:一旦其中一個(gè)寄生晶體管(比如Q2)開始導(dǎo)通,它的集電極電流會(huì)增加�。這個(gè)電流流過對(duì)應(yīng)的寄生電阻(Rnwell),產(chǎn)生壓降���。這個(gè)壓降會(huì)正向偏置另一個(gè)寄生晶體管(Q1)的發(fā)射結(jié)�����,導(dǎo)致Q1導(dǎo)通��。Q1導(dǎo)通后���,其集電極電流流過Rpsub,產(chǎn)生的壓降又加強(qiáng)了Q2的導(dǎo)通����。這個(gè)過程互為因果,迅速放大���。

4)閂鎖形成: 在極短時(shí)間內(nèi)�,正反饋使得兩個(gè)寄生晶體管都進(jìn)入深度飽和導(dǎo)通狀態(tài)���。此時(shí)�,電源VDD通過P+區(qū)->PMOS的寄生路徑(主要是Q1)->襯底->Q2->N+區(qū)到達(dá)地GND��,形成一條非常低阻的通路�。巨大電流開始流通。

5)狀態(tài)維持:一旦進(jìn)入這個(gè)導(dǎo)通狀態(tài),整個(gè)寄生SCR可以自我維持導(dǎo)通��,即使觸發(fā)源已經(jīng)消失����。此時(shí)唯一的停止方法是切斷電源(斷電重啟)。如果電流過大或持續(xù)時(shí)間過長(zhǎng)�,芯片就將因過熱而永久損壞。

總結(jié)關(guān)鍵點(diǎn):

- 元兇是CMOS工藝固有的寄生PNPN結(jié)構(gòu)(SCR)����。

- 觸發(fā)需要外部刺激來開啟其中一個(gè)寄生雙極管。

- 致命的正反饋回路導(dǎo)致電流雪崩式增長(zhǎng)�����。

- 一旦建立����,自維持且只能斷電解除。

三��、器件閂鎖效應(yīng)的內(nèi)因

雖然閂鎖由外部刺激觸發(fā)�,但CMOS器件本身的結(jié)構(gòu)和材料特性決定了其固有的閂鎖敏感性(Latch-up Immunity/Susceptibility)。主要內(nèi)部因素包括:

晶圓襯底電阻率(P-sub Resistivity)

P型襯底的電阻率越高����,其寄生電阻Rpsub越大��。這意味著同樣的觸發(fā)電流流過它時(shí),產(chǎn)生的壓降更大�,更容易使橫向NPN管(Q2)的基極-發(fā)射結(jié)正偏導(dǎo)通。因此����,高阻襯底會(huì)顯著降低CMOS器件的閂鎖耐受能力。

N阱電阻率 (N-well Resistivity)

與高阻襯底類似����,N阱的電阻率越高,Rnwell越大�,同樣的阱電流產(chǎn)生的壓降越大,更容易使縱向PNP管(Q1)的發(fā)射結(jié)正偏導(dǎo)通��。高阻N阱也不利于閂鎖防護(hù)�。

N阱深度 (N-well Depth) & P+到阱邊緣距離

P+擴(kuò)散區(qū)(PMOS源漏)離N阱邊緣越近,縱向PNP管(Q1)的基區(qū)(N阱)寬度就越窄�����。對(duì)于雙極管��,基區(qū)越窄其電流增益(β)通常越高。β值越高��,維持閂鎖所需的電流越小��,正反饋越容易形成和維持����,器件抗閂鎖能力越差。

N+到襯底接觸距離 (N+ to Sub Contact Spacing)

N+擴(kuò)散區(qū)(NMOS源漏)到最近的P+襯底接觸孔的距離越遠(yuǎn)�,則襯底電流流回地的路徑上,寄生電阻Rpsub的有效值越大����。這使得襯底上更容易積累電位差,導(dǎo)致橫向NPN管(Q2)的基極-發(fā)射結(jié)正偏�,抗閂鎖能力下降。

器件版圖布局的緊湊程度

隨著工藝尺寸不斷縮?����。柖桑?����,NMOS和PMOS管之間的距離越來越近�。這相當(dāng)于縮短了寄生SCR內(nèi)部各區(qū)域的物理距離���。其后果是:

寄生雙極管的基區(qū)寬度(WB)變窄 → 電流增益β增大→ 更容易發(fā)生閂鎖。

襯底或阱內(nèi)電流流向接觸孔的路徑電阻增大 → Rpsub/Rnwell增大→ 觸發(fā)電壓/電流降低 → 更容易被觸發(fā)����。

因此,工藝節(jié)點(diǎn)越先進(jìn)(尺寸越?��。酒旧砉逃械拈V鎖風(fēng)險(xiǎn)相對(duì)越高���,對(duì)設(shè)計(jì)防護(hù)的要求也越嚴(yán)格��。

制造工藝波動(dòng)(Process Variation)

摻雜濃度不均勻����、結(jié)深偏差�、接觸孔質(zhì)量等工藝波動(dòng),會(huì)影響寄生電阻和晶體管增益����,導(dǎo)致不同批次甚至同一芯片上不同區(qū)域的閂鎖閾值存在差異,增加預(yù)測(cè)和控制的難度����。

四����、如何抑制閂鎖效應(yīng)

從CMOS器件內(nèi)因出發(fā)如何提升其抗閂鎖能力呢����?這就需要從芯片的設(shè)計(jì)、制造工藝����、測(cè)試等多個(gè)環(huán)節(jié)協(xié)同發(fā)力。

1)芯片設(shè)計(jì)層面(Design Level)

增加阱和襯底接觸(Guard Rings):這是最核心的設(shè)計(jì)手段����。

環(huán)繞式接觸:在關(guān)鍵電路(如I/O驅(qū)動(dòng)器)周圍的N阱和P襯底中,密集布置大量的接觸孔(Contact)����。N阱接觸孔連接到VDD(通常通過低阻金屬線),P襯底接觸孔連接到GND����。

作用原理:大大降低Rnwell和Rpsub的阻值。當(dāng)有觸發(fā)電流試圖在襯底或阱中形成正偏壓時(shí)����,就近的接觸孔能迅速吸收這些電荷(通過VDD或GND泄放)����,有效壓低寄生晶體管基極的電位����,阻止其開啟或削弱正反饋強(qiáng)度。這就像在火藥桶周圍設(shè)置了高效的泄洪渠����。

采用保護(hù)環(huán)結(jié)構(gòu)(Double Guard Rings):

針對(duì)高風(fēng)險(xiǎn)區(qū)域����,采用N+/P+雙環(huán)結(jié)構(gòu),進(jìn)一步提升電荷抽取能力����。

加大關(guān)鍵間距:

• 增加PMOS P+ 到 N阱邊緣的距離:加大Q1的基區(qū)寬度,降低其β值����。

• 減小NMOS N+ 到 P+襯底接觸的距離:減小Rpsub。

• 確保N阱接觸靠近PMOS器件:減小Rnwell

優(yōu)化電源/地網(wǎng)絡(luò):

使用寬金屬線����、多層金屬布線����、足夠的通孔����,確保電源和地網(wǎng)絡(luò)的阻抗極低,有助于全局電荷泄放����。

使用SOI (Silicon-On-Insulator) :

SOI晶圓在頂層硅和襯底之間有一層埋氧絕緣層(BOX)。這層絕緣層徹底物理隔離了NMOS和PMOS器件����,從根本上消除了寄生PNPN結(jié)構(gòu)的存在。因此����,SOI工藝具有超強(qiáng)(甚至免疫)的閂鎖抗性,但成本相對(duì)較高����。

布局隔離 (Layout Isolation):將易觸發(fā)部分(如大型I/O緩沖器)與高敏感核心邏輯區(qū)用保護(hù)環(huán)或隔離區(qū)物理分開。

2)制造工藝層面(Process Level)

降低襯底/阱電阻率 (Low Substrate/N-well Resistivity):

通過精確控制摻雜濃度����,使用略低阻值的襯底材料����,或在阱下增加埋層(Buried Layer)形成低阻通路(需要特殊工藝如BiCMOS)����,減小RRpsub和Rnwell。

增加阱深度與結(jié)深:

在可行范圍內(nèi)����,增加N阱深度和P+結(jié)深,加寬Q1的基區(qū)����,降低其β值����。但這可能與先進(jìn)工藝的微縮化趨勢(shì)沖突。

優(yōu)化注入及退火工藝:確保摻雜分布均勻����、結(jié)輪廓陡峭,控制好寄生參數(shù)����。

3)測(cè)試與篩選層面(Test & Screening Level)

閂鎖觸發(fā)測(cè)試(Latch-up Test):通常在晶圓級(jí)或封裝級(jí)進(jìn)行����。依據(jù)JEDEC (JESD78) 等標(biāo)準(zhǔn)����,對(duì)芯片施加特定的電壓/電流應(yīng)力,如:

• I-test: 向引腳注入電流(±100mA)同時(shí)抬升/降低電源電壓(如VDD+25%/-25%)����。

• VDD overvoltage test: 施加過高的電源電壓。

測(cè)試過程中嚴(yán)密監(jiān)測(cè)電源電流����。如果電流持續(xù)異常增大(超過指定閾值或無法恢復(fù)),則判定樣品發(fā)生閂鎖����,該批次可能存在設(shè)計(jì)或工藝問題。

篩選標(biāo)準(zhǔn):測(cè)試條件需覆蓋芯片規(guī)格書規(guī)定的應(yīng)用范圍(電壓����、溫度)。只有通過嚴(yán)格閂鎖測(cè)試的芯片,才被認(rèn)定為可靠����。

五、如何避免應(yīng)用CMOS器件時(shí)的閂鎖效應(yīng)

對(duì)于負(fù)責(zé)器件選型和系統(tǒng)設(shè)計(jì)的工程師來說����,需要從“外部應(yīng)用”角度來規(guī)避閂鎖風(fēng)險(xiǎn):

1)器件選型:

核心指標(biāo):確認(rèn)其閂鎖特性。理想的情況是明確標(biāo)注符合JESD78標(biāo)準(zhǔn)(例如����,注明通過了Class I, II等級(jí)別的測(cè)試,通常Class I/II要求更嚴(yán)格)����,并提供最小觸發(fā)電流ITRIG和最大維持電流IHOLD(參數(shù)值越大越好)。

安全選擇:對(duì)于高可靠性應(yīng)用(如工業(yè)控制����、汽車電子、醫(yī)療設(shè)備)����,優(yōu)先選擇明確標(biāo)注“Latch-up immune per JESD78 Class X”或“SOI工藝”的器件����。

警惕:如果數(shù)據(jù)手冊(cè)中關(guān)于閂鎖的信息模糊不清或缺失����,務(wù)必向供應(yīng)商(FAE)確認(rèn)����。規(guī)避風(fēng)險(xiǎn)不明的器件。

2)系統(tǒng)應(yīng)用設(shè)計(jì)注意事項(xiàng):

“數(shù)據(jù)手冊(cè)是圣經(jīng)”:務(wù)必嚴(yán)格遵守?cái)?shù)據(jù)手冊(cè)推薦的:

- 最大工作電壓/瞬時(shí)電壓上限:任何引腳上的電壓不要超過其規(guī)定的絕對(duì)最大值(通常VSS-0.3V ~ VDD+0.3V是一個(gè)常見邊界����,需仔細(xì)核對(duì))。超壓是強(qiáng)觸發(fā)源����!

- 電源電壓范圍:保證應(yīng)用電壓(VCC/VDD/Vin等)在允許范圍內(nèi),避免過壓或欠壓����。

- 最大輸入/輸出電流: 避免驅(qū)動(dòng)能力超限導(dǎo)致內(nèi)部結(jié)過載

。

- 工作溫度范圍:避免器件在超溫下運(yùn)行����。

采用推薦/必需的防護(hù)電路:

- 系統(tǒng)限流:在外部電源和芯片之間加入熔斷保險(xiǎn)絲(Fuse)或可復(fù)位保險(xiǎn)絲(PTC)。一旦發(fā)生閂鎖導(dǎo)致電流劇增����,保險(xiǎn)絲會(huì)及時(shí)熔斷或阻值劇增����,切斷電源通路����,保護(hù)芯片不被燒毀。

- 芯片電源:尤其對(duì)于從外部取電或易受干擾的接口板����,在靠近芯片電源引腳處并聯(lián)去耦電容(濾除高頻噪聲)和TVS管(吸收大浪涌)。遵循“入口處防護(hù)”原則����。

- 電源穩(wěn)定性:保證系統(tǒng)電源穩(wěn)定、紋波小����,避免劇烈的上電/掉電速率(dV/dt)。必要時(shí)為敏感芯片配置獨(dú)立的LDO穩(wěn)壓器����。

- 接地良好: 確保整個(gè)系統(tǒng)的接地網(wǎng)絡(luò)阻抗低且設(shè)計(jì)良好,設(shè)計(jì)短而粗的地線(減小阻抗)����,單點(diǎn)接地或采用星型接地策略以降低回流路徑阻抗差異,避免因地彈(Ground Bounce)等問題引入潛在觸發(fā)����。

- 輸入端:必要時(shí)在可能引入干擾的信號(hào)線(如長(zhǎng)線接口、按鍵����、與繼電器或電機(jī)接口處)串入限流電阻或在信號(hào)線對(duì)地加鉗位二極管。

- 上電/掉電順序:復(fù)雜的多電源系統(tǒng)中����,不同電源軌的上電/掉電順序可能引起閂鎖。如果器件手冊(cè)有要求����,使用電源管理IC或時(shí)序控制電路保證符合順序。

- 熱插拔設(shè)計(jì):除非芯片明確支持(有內(nèi)部保護(hù))����,否則盡量避免對(duì)帶電插拔部件(如接口卡、模塊)在系統(tǒng)運(yùn)行中進(jìn)行插拔操作����。

- 熱管理:避免芯片長(zhǎng)期工作在高溫環(huán)境����,因?yàn)楦邷貢?huì)降低寄生管的觸發(fā)閾值����,更容易發(fā)生閂鎖。良好的散熱設(shè)計(jì)和溫度監(jiān)控是必要的����。

ESD防護(hù)不容忽視:

良好的ESD防護(hù)不僅保護(hù)端口,也降低了觸發(fā)閂鎖的風(fēng)險(xiǎn)����。確保生產(chǎn)、組裝����、維修過程中人員接地及設(shè)備符合ESD安全規(guī)范。關(guān)鍵外接端口應(yīng)有ESD保護(hù)器件����。

仿真分析: 如果條件允許,使用EDA工具對(duì)關(guān)鍵信號(hào)路徑的完整性(信號(hào)噪聲����、振鈴)和電源分布網(wǎng)絡(luò)(阻抗����、噪聲)進(jìn)行仿真����,識(shí)別潛在的電壓過沖風(fēng)險(xiǎn)點(diǎn)����。

六、結(jié)語(yǔ)

閂鎖效應(yīng)是CMOS技術(shù)發(fā)展道路上必須跨越的一道屏障����。通過深入理解其內(nèi)部寄生SCR機(jī)制,利用先進(jìn)的設(shè)計(jì)規(guī)則����、工藝改進(jìn)、嚴(yán)格的測(cè)試篩選����,以及在系統(tǒng)應(yīng)用層面(限流、浪涌保護(hù)����、熱管理)的綜合防護(hù)措施����,現(xiàn)代半導(dǎo)體工業(yè)已能極大地馴服這個(gè)“開關(guān)幽靈”����。對(duì)于工程師而言,選擇符合可靠標(biāo)準(zhǔn)的器件����,并嚴(yán)格遵循設(shè)計(jì)規(guī)范和應(yīng)用限制,是保障電子系統(tǒng)長(zhǎng)期穩(wěn)定運(yùn)行的基石����。

![Wang: [圖片] Wang: CMOS閂鎖效應(yīng)及失效分析](/uploads/ad/weixin20151213185125.png )