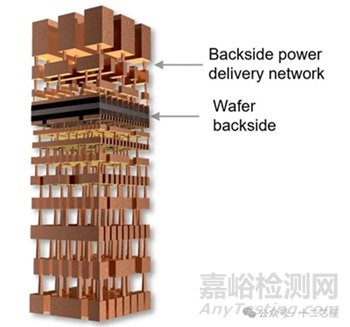

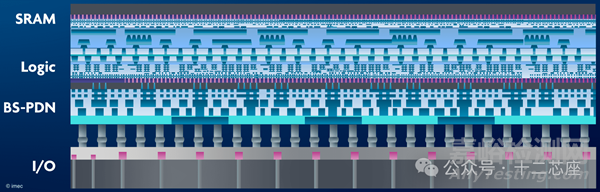

在追求更高性能��、更低功耗和更高密度晶體管陣列的競(jìng)爭(zhēng)中���,半導(dǎo)體制造商正在積極擁抱一項(xiàng)名為“背面供電網(wǎng)絡(luò)”(BSPDN)的根本性架構(gòu)變革�����。這項(xiàng)技術(shù)將供電從傳統(tǒng)的正面(已擠滿了邏輯和信號(hào)布線)轉(zhuǎn)移到晶圓背面��,從而為高密度晶體管邏輯騰出寶貴的空間。

然而�����,這項(xiàng)革命性的進(jìn)步帶來(lái)了全新的套刻和工藝控制挑戰(zhàn),如果處理不當(dāng)����,可能會(huì)顯著影響良率、成本和上市時(shí)間��。應(yīng)用材料公司正在率先推出新一代計(jì)量解決方案�����,旨在利用電子束 (ebeam) 的優(yōu)勢(shì),應(yīng)對(duì)這些新興挑戰(zhàn)��。

顛覆性技術(shù)帶來(lái)新的計(jì)量挑戰(zhàn)

背面功率概念涉及制造互連(稱為背面通孔),從晶圓背面穿過(guò)硅襯底�����,直接連接到晶體管級(jí)結(jié)構(gòu)(例如源極/漏極)��。其主要優(yōu)勢(shì)是顯著降低電阻�、縮短電流路徑并提高晶體管密度,所有這些都有助于提升先進(jìn)邏輯���、AI 處理器和下一代移動(dòng)設(shè)備的每瓦性能。

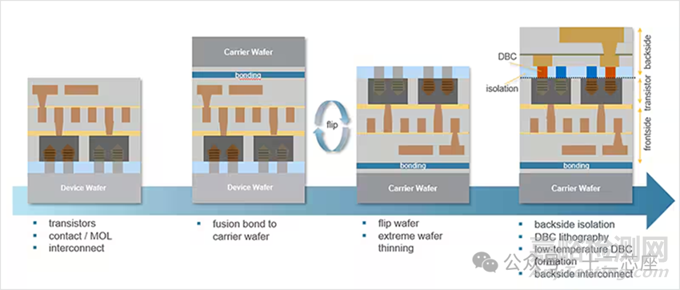

但集成這種新型架構(gòu)需要復(fù)雜的晶圓鍵合工藝和額外的高精度制造步驟�����。具體來(lái)說(shuō),它需要將載體晶圓鍵合到正面�,翻轉(zhuǎn)晶圓��,將其減薄至10微米以下的厚度�,然后將背面觸點(diǎn)圖案化并對(duì)準(zhǔn)先前制造的正面器件層����。這些額外的晶圓處理和鍵合步驟顯著增加了疊層工藝的復(fù)雜性����,并帶來(lái)了諸多挑戰(zhàn)�����,例如:

鍵合��、減薄和拋光步驟引起的晶圓變形和應(yīng)力

由于背面加工遮擋了隱藏的正面參考層,導(dǎo)致對(duì)準(zhǔn)困難

晶圓因圖案而變形���,產(chǎn)生難以預(yù)測(cè)和補(bǔ)償?shù)姆蔷€性疊加誤差

如果沒有精確的覆蓋控制���,背面通孔和晶體管級(jí)結(jié)構(gòu)之間即使出現(xiàn)最輕微的納米級(jí)錯(cuò)位����,也會(huì)嚴(yán)重影響器件性能����、可靠性和產(chǎn)量。

傳統(tǒng)的疊加方法已不再足夠

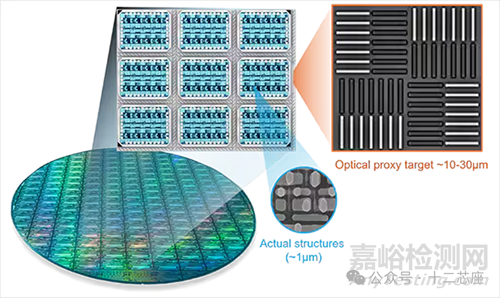

歷史上�����,晶圓廠一直依賴于光學(xué)套刻測(cè)量技術(shù),使用放置在有源器件區(qū)域之外的大型替代目標(biāo)�����。但隨著背面功率的增加����,這些目標(biāo)越來(lái)越難以代表實(shí)際的器件級(jí)套刻�����。當(dāng)背面接觸直接接觸微小的晶體管級(jí)特征(例如構(gòu)成最新環(huán)繞柵極晶體管基礎(chǔ)的納米片堆疊)時(shí),這種脫節(jié)會(huì)變得更加嚴(yán)重��。簡(jiǎn)而言之����,傳統(tǒng)方法無(wú)法可靠地檢測(cè)出決定最先進(jìn)節(jié)點(diǎn)成敗的納米級(jí)套刻誤差��。

下一代電子束計(jì)量技術(shù)的需求

為了應(yīng)對(duì)這些前所未有的挑戰(zhàn)�,晶圓廠迫切需要前所未有的精度�、分辨率和效率來(lái)測(cè)量背面直接接觸疊層��,以捕捉背面通孔和納米片之間真實(shí)的器件級(jí)對(duì)準(zhǔn)情況。目前的熱場(chǎng)發(fā)射 (TFE) 設(shè)備不足以實(shí)現(xiàn)背面功率和 GAA 晶體管架構(gòu)芯片的大批量生產(chǎn)��。業(yè)界需要新一代電子束測(cè)量技術(shù)來(lái)實(shí)現(xiàn)一系列改進(jìn):

更高的分辨率:

需要更高的精度來(lái)準(zhǔn)確捕捉細(xì)微的覆蓋偏移和納米級(jí)錯(cuò)位,這對(duì)于控制落在復(fù)雜堆棧下方的納米片或柵極結(jié)構(gòu)上的背面接觸至關(guān)重要����。

更高的速度:

變形和所需的校正非常復(fù)雜——遠(yuǎn)遠(yuǎn)超出了基本的偏移或移位。這需要更大規(guī)模的計(jì)量�����,每個(gè)晶圓的測(cè)量次數(shù)將增加10到100倍��。更高的速度至關(guān)重要�,因?yàn)橛?jì)量步驟不能延長(zhǎng)。

更高的能量:

下一代量測(cè)工具需要以更高的注入能量(高達(dá) 60 keV)運(yùn)行���,以便深入穿透復(fù)雜的 3D 堆疊��。這允許直接測(cè)量背面通孔相對(duì)于正面晶體管級(jí)特征的位置�,而無(wú)需進(jìn)行破壞性橫截面分析,從而直接提高先進(jìn)背面功率網(wǎng)絡(luò)的良率����。

更高效地收集背散射電子 (BSE):

先進(jìn)的 BSE 探測(cè)器技術(shù)可顯著提高收集效率�,提供更佳的材料對(duì)比度���,并更清晰地成像埋層結(jié)構(gòu)。高質(zhì)量的 BSE 信號(hào)能夠可靠地檢測(cè)多層 3D 集成結(jié)構(gòu)中細(xì)微的疊層錯(cuò)位�。

先進(jìn)的輪廓提取算法:

為了補(bǔ)充先進(jìn)的成像功能�,下一代工具需要強(qiáng)大的圖像增強(qiáng)���、降噪和輪廓提取算法���。這些先進(jìn)的軟件工具在提升測(cè)量精度的同時(shí)����,克服了電子束引起的充電難題��,能夠精確地測(cè)量納米片結(jié)構(gòu)上的背面觸點(diǎn)——而這正是傳統(tǒng)光學(xué)工具難以實(shí)現(xiàn)的����。

應(yīng)對(duì)這些挑戰(zhàn)�����,芯片制造商能夠直接測(cè)量背面觸點(diǎn)與晶體管特征之間的疊對(duì)�����,在制造工藝早期識(shí)別晶圓級(jí)變形和應(yīng)力引起的錯(cuò)位����,并實(shí)現(xiàn)對(duì)背面通孔放置的更嚴(yán)格的工藝控制——所有這些都可以顯著減少疊對(duì)誤差����,從而對(duì)工藝良率產(chǎn)生實(shí)際影響。

具有背面供電實(shí)現(xiàn)的 3D-SOC 示意圖

Process FLOW

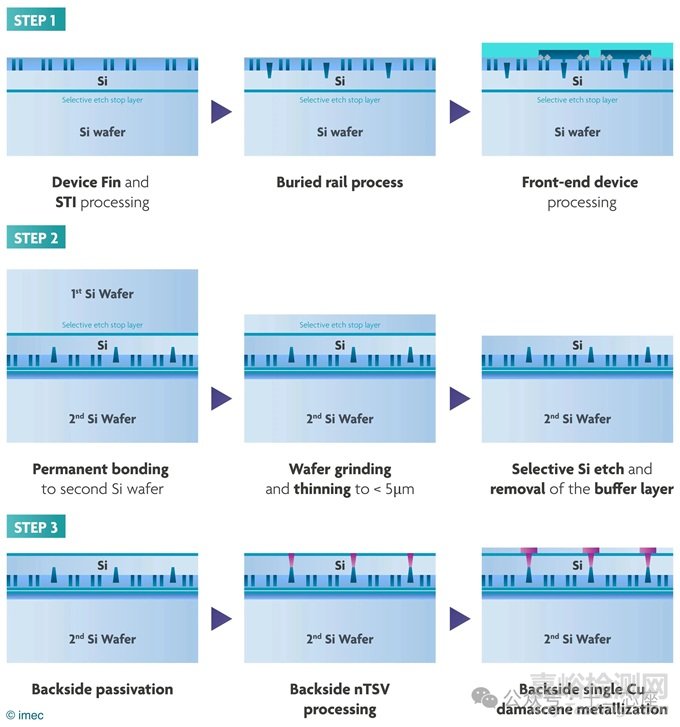

下面�,詳細(xì)闡述BSPDN的具體實(shí)現(xiàn)工藝流程����,其中nTSV(在極薄的晶圓背面加工)位于BPR之上����。例如�����,在晶圓正面加工的微縮FinFET器件,通過(guò)BPR和nTSV連接到晶圓背面�����。

From: IMEC

步驟 1:采用埋軌進(jìn)行正面處理

該工藝流程始于在 300 毫米硅晶圓頂部生長(zhǎng)一層 SiGe 層。SiGe 層隨后作為蝕刻停止層�����,以結(jié)束晶圓減?���。ú襟E 2)����。接下來(lái),在 SiGe 層頂部生長(zhǎng)一層薄硅覆蓋層:這是制造器件和埋入式電源軌的起點(diǎn)。埋入式電源軌在淺溝槽隔離后定義��。在硅覆蓋層中蝕刻的溝槽用氧化物襯墊和金屬(例如 W 或 Ru)填充���。由此產(chǎn)生的埋入式電源軌通常寬度約為 30 納米,間距約為 100 納米��。然后將金屬凹陷并用電介質(zhì)覆蓋����。在 BPR 實(shí)現(xiàn)后���,器件(在本例中為縮放的 FinFET)的加工完成�,并且 BPR 通過(guò) VBPR 通孔和 M0A 線連接到晶體管的源極/漏極區(qū)域����。銅金屬化完成了正面加工。

步驟2:晶圓間鍵合和晶圓減薄

將包含器件和BPR的晶圓翻轉(zhuǎn)�����,將“有源”正面鍵合到毯式載體晶圓上�。這一過(guò)程在室溫下采用SiCN-SiCN電介質(zhì)熔融鍵合�����,然后在250°C下進(jìn)行鍵合后退火。然后��,將第一片晶圓的背面減薄至SiGe蝕刻停止層的位置��。減薄過(guò)程通過(guò)依次進(jìn)行背面研磨���、化學(xué)機(jī)械拋光(CMP)以及干濕蝕刻步驟來(lái)實(shí)現(xiàn)���。下一步是去除SiGe層���,然后晶圓即可進(jìn)行nTSV工藝�。

步驟 3:nTSV 處理并連接到 BPR

在沉積背面鈍化層后��,通過(guò)硅對(duì)準(zhǔn)光刻工藝從晶圓背面對(duì)nTSV 進(jìn)行圖案化�。nTSV 蝕刻穿過(guò)硅(深度達(dá)數(shù)百納米)�����,并落在 BPR 的尖端���。接下來(lái)�,用氧化物襯墊和金屬(鎢)填充nTSV�。在此具體實(shí)現(xiàn)中,它們以 200 納米間距集成���,不會(huì)占用標(biāo)準(zhǔn)單元的任何面積。該流程通過(guò)處理一層或多層背面金屬層來(lái)完成�����,通過(guò) nTSV 將晶圓背面與正面的 BPR 電連接�����。

免責(zé)聲明:作者尊重知識(shí)產(chǎn)權(quán)����、部分圖片和內(nèi)容來(lái)源于公開網(wǎng)絡(luò)��,版權(quán)歸原撰寫發(fā)布機(jī)構(gòu)所有�����,如涉及侵權(quán)����,請(qǐng)及時(shí)聯(lián)系刪除。

Reference:1.B. Cline et al., ‘Power from below: buried interconnects will help save Moore's Law,’ in IEEE Spectrum, vol. 58, no. 9, pp. 46-51, September 2021, doi: 10.1109/MSPEC.2021.95310122.‘Arm shows backside power delivery as path to further Moore’s Law’, IEEE Spectrum, 20193.A. Veloso et al., ‘Enabling logic with backside connectivity via n-TSVs and its potential as a scaling booster’, 2021 Symposium on VLSI Technology, 2021, pp. 1-2