目錄

[CH.1]:Shallow Trench Isolation(STI)Gapfill不良

[CH.2]:Seam不良[CH.3]:Particle 引起的不良

[CH.4]:Deposition Uniformity不良

[CH.5]:Silicide Encroachment / Silicide Stringer不良

[CH.6]:Overhang不良

[CH.7]:Poor Stepp Coverage不良

[CH.8]:絕緣膜的開(kāi)裂(Crack)缺陷

[CH.9]:Gate Oxide Thinning不良

[CH.10]:Not Open不良

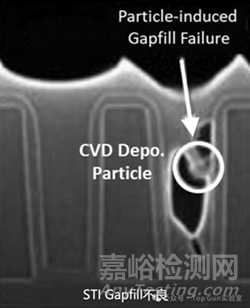

【CH.1】Shallow Trench Isolation(STI)Gapfill不良

第一類不良議題是 STI(淺溝槽隔離)填充不良。隔離工藝可分為溝槽隔離(Trench Isolation)和結(jié)隔離(Junction Isolation)��。尤其對(duì)溝槽隔離而言���,它既通過(guò)拉開(kāi)相鄰器件的物理間距來(lái)定義晶體管的器件域(domain)���,又承擔(dān)電學(xué)隔離功能。然而在形成 STI 時(shí)���,如果如圖所示沉積(deposition)工藝能力不足�����,因開(kāi)口處的 overhang 或溝槽輪廓內(nèi)的顆粒使得填充(gapfill)不完全�����,就會(huì)形成空洞(void)���,造成相鄰器件之間的場(chǎng)區(qū)漏電(field leakage)��。結(jié)果會(huì)使器件特性離散度增大或發(fā)生失配(mismatch)��;嚴(yán)重時(shí)��,器件會(huì)出現(xiàn)硬失效(hard fail)而無(wú)法正常工作��。隨著制程持續(xù)微縮���,沉積工藝對(duì)高難度 gapfill 技術(shù)的需求愈發(fā)提高。

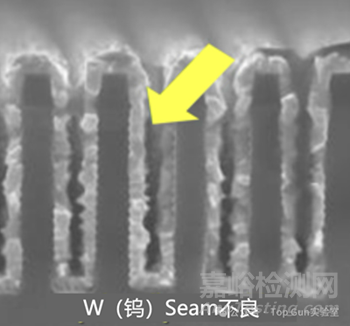

【CH.2】Seam不良

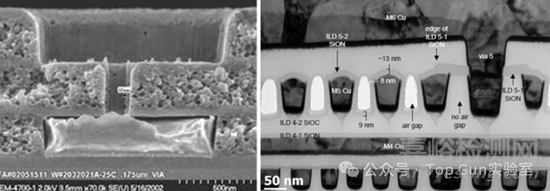

第二個(gè)是不良 Seam 縫隙缺陷���。Seam 與 Void 共同的特點(diǎn)是由于高寬深比 (High AR) 的 Gapfill 能力下降以及 Step Coverage 較差而產(chǎn)生的不良類型�����。(可以簡(jiǎn)單理解為它們只是形態(tài)上的差異�����,當(dāng) Seam 縫隙嚴(yán)重時(shí)就會(huì)演變?yōu)?Void 空洞)���。特別是在先進(jìn)制程中,為了在一顆芯片內(nèi)實(shí)現(xiàn)高密度與多功能�����,會(huì)集成無(wú)數(shù)個(gè)晶體管 (Tr.) 于 IC 中。為了實(shí)現(xiàn)其電學(xué)功能�����,就必須形成大量的 Contact/Via 以及復(fù)雜的金屬布線 (Metal Routing)�����。因此���,為了連接上下層薄膜之間的金屬線而形成的 Contact/Via 孔,其剖面結(jié)構(gòu)越來(lái)越呈現(xiàn)高寬深比 (High AR Profile)���。如果像上圖所示的鎢 (W) 金屬?zèng)]有被正確填充 (Gapfill)���,則會(huì)導(dǎo)致電阻增加,從而引發(fā)失效�����。因此��,需要具備優(yōu)異 Step Coverage 特性的高難度沉積工藝技術(shù)。

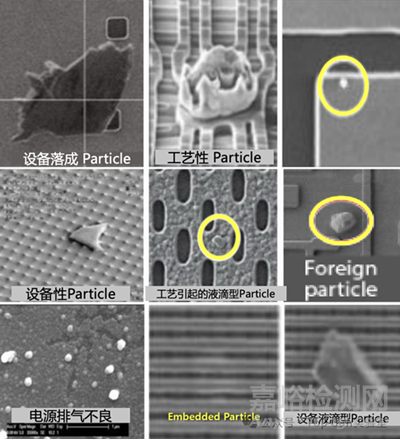

【CH.3】Particle 引起的不良

由顆粒(Particle)引起的異物性缺陷通常在 Wafer Map 上呈現(xiàn)隨機(jī)分布��,大多數(shù)表現(xiàn)為硬性失效(Hard Fail)�����,因此需要強(qiáng)化 CIP(持續(xù)改善活動(dòng))來(lái)降低顆粒的發(fā)生���。顆粒缺陷一般會(huì)導(dǎo)致金屬線間的短路�����,或在 Contact/VIA Hole 中產(chǎn)生 Void��,從而引發(fā)開(kāi)路(Open)失效�����。此外��,如果在存在顆粒的狀態(tài)下進(jìn)行沉積工藝��,受到偏壓(Bias)或在沉積過(guò)程中���,顆粒所在區(qū)域可能會(huì)釋放應(yīng)力或揮發(fā)性氣體�����,進(jìn)而引起針孔(Pinhole)缺陷��。由于顆粒引起的缺陷大多為硬性失效(Hard Fail)���,除了作為工程師必須保持制造工藝環(huán)境的清潔外,幾乎沒(méi)有其他補(bǔ)救措施��。而且在良率損失(Yield Loss)中占比很高�����,因此至關(guān)重要���。

通常,顆粒缺陷可以分為三類:

1.設(shè)備性顆粒(Equipment-induced Particle)

2.工藝反應(yīng)性顆粒(Process-induced Particle)

3.外來(lái)顆粒(External Particle)

從上圖也可以推斷��,設(shè)備引起的顆粒一般出現(xiàn)在晶圓邊緣(Edge)部分�����,提示設(shè)備的 PM(預(yù)防性維護(hù))與排氣狀態(tài)不適當(dāng),同時(shí)需要重新檢查設(shè)備輸入?yún)?shù)��。工藝反應(yīng)過(guò)程中產(chǎn)生的顆粒�����,通常呈現(xiàn)圓形(Round Shape)��,可能由于設(shè)備故障或工藝條件未優(yōu)化而導(dǎo)致��。最后一種是非反應(yīng)性或設(shè)備性�����,而是來(lái)自外部環(huán)境的顆粒���。當(dāng)在顆粒上方形成光刻圖形時(shí)�����,由于顆粒殘留在圖形下方的膜層中�����,會(huì)造成表面高度差(Step Height)�����,從而影響上層圖形的完整性�����。因此�����,設(shè)備的PM周期���、工藝條件的優(yōu)化以及清潔的工藝環(huán)境都是控制顆粒缺陷的關(guān)鍵��。

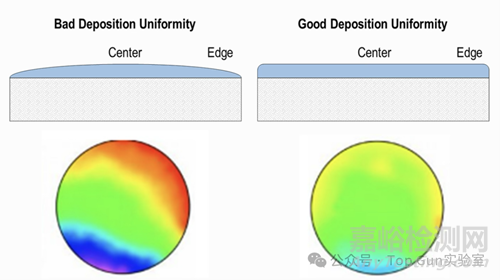

【CH.4】Deposition Uniformity不良

在沉積(Deposition)過(guò)程中�����,晶圓(Wafer)上的均勻性不良可能會(huì)導(dǎo)致器件特性的變化,并在后續(xù)工藝中引發(fā)開(kāi)路/短路(Open/Short)等缺陷�����。工藝工程師需要在工藝配方(Recipe)中優(yōu)化工藝溫度��、壓力等沉積條件,同時(shí)必須改善晶圓上的 L/B/C/T/R/LT/LB/RB/RT 等位置的均勻性�����。換句話說(shuō)�����,根據(jù)晶圓位置來(lái)優(yōu)化均勻的沉積速率(Depo. rate)是沉積工藝工程師的職責(zé)���。晶圓中心(Center)與邊緣(Edge)之間的均勻性(In Wafer Uniformity)不僅在沉積工藝中至關(guān)重要���,在光刻(Photo)、化學(xué)機(jī)械拋光(CMP)�����、刻蝕(Etch)工藝中同樣是關(guān)鍵挑戰(zhàn)�����。尤其是隨著微細(xì)工藝的到來(lái)��,其重要性進(jìn)一步提高��。在沉積(Deposition)過(guò)程中,晶圓(Wafer)上的均勻性不良可能會(huì)導(dǎo)致器件特性的變化���,并在后續(xù)工藝中引發(fā)開(kāi)路/短路(Open/Short)等缺陷�����。工藝工程師需要在工藝配方(Recipe)中優(yōu)化工藝溫度���、壓力等沉積條件,同時(shí)必須改善晶圓上的 L/B/C/T/R/LT/LB/RB/RT 等位置的均勻性��。換句話說(shuō)�����,根據(jù)晶圓位置來(lái)優(yōu)化均勻的沉積速率(Depo. rate)是沉積工藝工程師的職責(zé)���。晶圓中心(Center)與邊緣(Edge)之間的均勻性(In Wafer Uniformity)不僅在沉積工藝中至關(guān)重要�����,在光刻(Photo)、化學(xué)機(jī)械拋光(CMP)�����、刻蝕(Etch)工藝中同樣是關(guān)鍵挑戰(zhàn)。尤其是隨著微細(xì)工藝的到來(lái)�����,其重要性進(jìn)一步提高���。

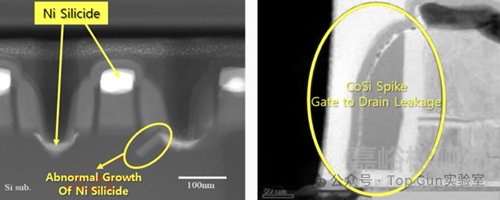

【CH.5】Silicide Encroachment / Silicide Stringer不良

硅化物(Silicide)工藝是為了降低由于金屬與半導(dǎo)體結(jié)之間功函數(shù)差異所形成的肖特基勢(shì)壘(Schottky Barrier)引起的高接觸電阻���。所謂自對(duì)準(zhǔn)硅化物工藝(Salicide, Self-Aligned Silicide)的基本流程可以簡(jiǎn)要描述如下:首先通過(guò) PVD(物理氣相沉積)在晶圓表面整體沉積 Co/Ti/Ni 金屬以及鈍化層(Capping Layer),隨后經(jīng)過(guò)退火(Annealing)處理��,使金屬原子向硅內(nèi)部擴(kuò)散(Diffusion)并形成硅化物層��。然而��,在實(shí)際工藝中���,硅化物可能會(huì)出現(xiàn)異常生長(zhǎng)(Encroachment)���,從而導(dǎo)致器件的結(jié)漏電(Junction Leakage)。這種問(wèn)題通常受到硅襯底摻雜(Doping)��、表面清洗(Surface Cleaning)、Ni 膜厚以及退火條件的顯著影響���。右側(cè)圖示中的硅化物 Stringer�����,指的是在器件側(cè)壁上殘留的硅化物殘?jiān)⊿ilicide Residue)���。這類殘?jiān)瑯訒?huì)在柵極(Gate)與漏極(Drain)之間形成漏電通道(Leakage Path),進(jìn)而影響器件性能���。

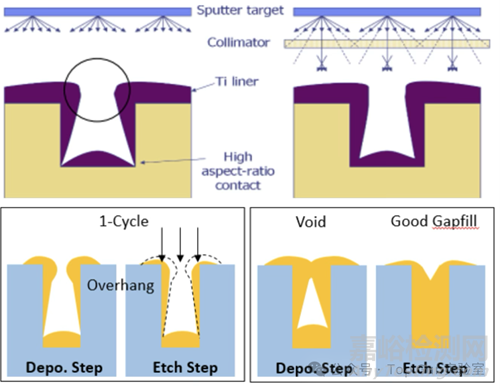

【CH.6】Overhang不良

當(dāng)出現(xiàn) Overhang(懸垂現(xiàn)象)時(shí)���,嚴(yán)重情況下會(huì)在下方形成 Void(空洞)。在 PVD(物理氣相沉積)工藝中�����,為了改善 Overhang 問(wèn)題���,通常會(huì)使用 Collimator(準(zhǔn)直器)來(lái)改善��。但在 Collimated Sputtering(準(zhǔn)直濺射)過(guò)程中��,顆粒會(huì)在 Collimator 上沉積�����,導(dǎo)致沉積速率下降���,因此需要定期更換。在 CVD(化學(xué)氣相沉積)工藝中���,為了改善 Overhang 問(wèn)題���,常采用 HDPCVD(高密度等離子體化學(xué)氣相沉積)工藝,并通過(guò) Depo-Sputtering 1-Cycle 的方式來(lái)實(shí)現(xiàn)��,該工藝多應(yīng)用于 Trench(溝槽)制程�����。然而��,由于等離子體密度過(guò)高���,可能會(huì)產(chǎn)生 Plasma Damage(等離子體損傷)引起的 Defect(缺陷)���,這可能進(jìn)一步導(dǎo)致 Hump(凸起)現(xiàn)象��,以及器件特性的 Variation(波動(dòng))和 Mismatch(失配)���。因此,為了使 STI(淺溝槽隔離)的薄膜更加致密���,有必要在后續(xù)工藝中進(jìn)行 Densification(致密化處理)��。

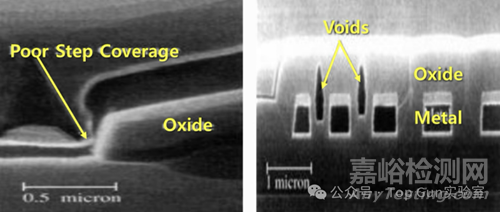

【CH.7】Poor Stepp Coverage不良

需要通過(guò)重新評(píng)估層間絕緣膜(Interlayer Dielectric, ILD)沉積配方(Deposition Recipe)以及更換材料�����,來(lái)提升 Step Coverage(步進(jìn)覆蓋率)并重新評(píng)估實(shí)現(xiàn)無(wú)空洞(Void Free)的工藝��。

【CH.8】絕緣膜的開(kāi)裂(Crack)缺陷

絕緣膜(Insulating Layer)在器件之間的層間隔離等方面起著重要作用���。特別是隨著微細(xì)工藝的發(fā)展,為了降低金屬線傳輸信號(hào)的 RC 延遲�����,在 ILD/IMD 層中采用了低介電常數(shù)(Low-k)材料技術(shù)。這些材料通過(guò)摻雜碳或人為形成多孔結(jié)構(gòu)甚至 Airgap(空氣隙)來(lái)實(shí)現(xiàn)低介電常數(shù)�����。然而��,由于多孔結(jié)構(gòu)的存在�����,這類材料在機(jī)械上非常脆弱���,容易產(chǎn)生開(kāi)裂(Crack)缺陷。

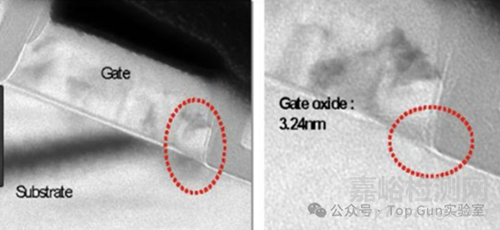

【CH.9】Gate Oxide Thinning不良

Gate Oxide(柵氧化層)的厚度是決定器件 Gox BV(Breakdown Voltage)��、可靠性 以及 Vth(閾值電壓) 特性的重要參數(shù)之一���。如上所述�����,Gate Oxide 的局部變薄現(xiàn)象在特定 LOT 的 Gate Oxide 工藝過(guò)程中��,需要嚴(yán)格檢查工藝前后是否存在異常情況���。(由于對(duì)器件特性極為關(guān)鍵���,這必然會(huì)影響產(chǎn)品的正常工作。)

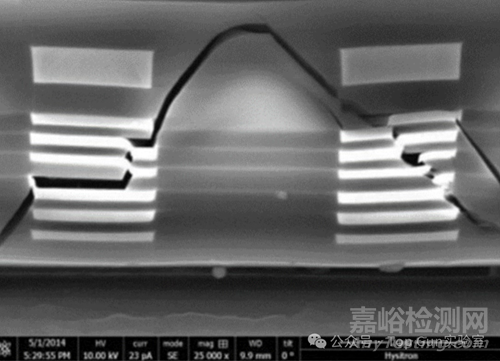

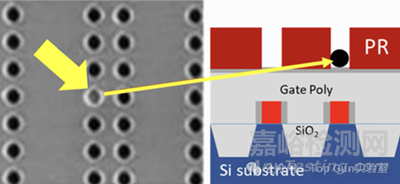

【CH.10】GNot Open不良

Not Open 缺陷是半導(dǎo)體芯片中典型的 Hard 故障類型之一��。特定 Contact 出現(xiàn) Not Open 現(xiàn)象時(shí)�����,需要考慮多種可能的原因��,包括顆粒(Particle)因素���、光刻對(duì)準(zhǔn)(Photo Align)問(wèn)題���、沉積均勻性(Deposition Uniformity)以及蝕刻均勻性(Etch Uniformity)等。在防止此類 Hard 故障的 Layout 設(shè)計(jì)上��,可以通過(guò)禁止單一 Contact/VIA 孔�����,而形成雙孔或更多孔的 Contact/VIA 來(lái)改善 Hard 故障引起的良率損失(Yield Loss)���。但是�����,如果將單一 Contact/VIA 增加為多個(gè)��,會(huì)導(dǎo)致 Chip 尺寸增大��,從而降低設(shè)計(jì)競(jìng)爭(zhēng)力���。