導(dǎo)語:靜電不可捉摸��,卻又無處不在。人們只有深刻認(rèn)識到靜電的危害和影響機(jī)理��,并在各個相關(guān)環(huán)節(jié)采取有效的靜電防護(hù)措施才能防范并降低電子產(chǎn)品的ESD失效風(fēng)險(xiǎn)��。

一��、半導(dǎo)體的ESD失效模式

電子產(chǎn)品因ESD可能引起半導(dǎo)體元器件損傷而導(dǎo)致失效或故障���。半導(dǎo)體器件的靜電損傷�����,有兩類模式���,即突發(fā)性完全失效和潛在性損傷。

ESD使元器件突發(fā)性完全失效的概率僅約10%�����,表現(xiàn)為短路、開路����、無功能、參數(shù)不符合要求等���;而90%情況下則是元器件遭受到潛在性輕微損傷�����,損傷后電參數(shù)仍能符合規(guī)定的使用要求���,但減弱了元器件抗過電應(yīng)力(EOS)的能力,在使用現(xiàn)場容易出現(xiàn)早期失效���。

1.1 突發(fā)性完全失效

突發(fā)性完全失效是器件的一個或多個電參數(shù)突然劣化,完全失去規(guī)定功能的一種失效���。通常表現(xiàn)為開路�����、短路以及電參數(shù)嚴(yán)重漂移�����。

半導(dǎo)體器件ESD損傷失效現(xiàn)象主要包括:

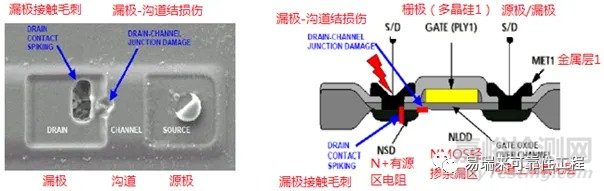

圖1. 介質(zhì)擊穿

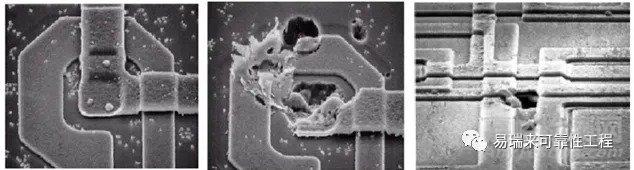

鋁互連線損傷與燒熔

硅片局部區(qū)域熔化

圖2. 硅半導(dǎo)體熱熔-鋁線熱熔

PN結(jié)損傷和熱破壞短路

擴(kuò)散電阻與多晶電阻損傷

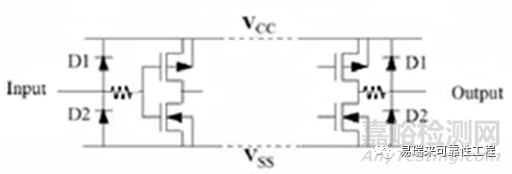

觸發(fā)CMOS“閂鎖(Latch-up)效應(yīng)”

對微電路中的一段線路做ESD實(shí)驗(yàn)發(fā)現(xiàn):

① 200V~400V時- 線路的阻抗沒有發(fā)現(xiàn)變化

② 600V時- 微電路的性能指標(biāo)稍有下降��,但仍能通過測試�����。

③ 800V~900V- 出現(xiàn)了局部熔斷和孔洞�����,線路阻抗發(fā)生了明顯變化

④ 1000V - 線路斷開�����,器件被完全損壞

圖3. 微電路ESD試驗(yàn)

1.2 潛在性損傷

如果帶電體的靜電勢或存儲的靜電能量較低���,或ESD回路有限流電阻存在�,一次ESD脈沖不足以引起器件發(fā)生突發(fā)性完全失效���,但它會在器件內(nèi)部造成輕微損傷����,這種損傷又是積累性的。隨著ESD脈沖次數(shù)增加��,器件的損傷閾值電壓逐漸下降��,器件的電參數(shù)逐漸劣化��,這類失效稱為潛在性失效��。潛在性失效的表現(xiàn)往往是器件的使用壽命縮短��,或者一個本來不會使器件損傷的小脈沖卻使該器件失效�����。潛在性失效降低了器件抗靜電的能力���,降低了器件的使用可靠性��。半導(dǎo)體器件潛在性失效主要表現(xiàn)為:

(1) 柵氧化層損傷

MOS柵氧化層受到ESD的作用,會產(chǎn)生細(xì)微損傷����,有時會導(dǎo)致柵極泄漏電流少量增加����。這種情況的發(fā)生可能是由于放電時形成絲狀鋁硅合金���,該合金尚不能跨接整個柵氧化物�����,使得受損的氧化層擊穿電壓降低���,在使用時就可能由于低能量EOS或者ESD使得已經(jīng)受損的氧化層擊穿,從而使器件失效�����。柵氧化層的擊穿機(jī)理�,目前認(rèn)為可分為兩個階段:

1)第一階段是建立階段,或形象稱為“磨損”階段�����。在電應(yīng)力作用下�����,氧化層內(nèi)部及Si-SiO2界面處發(fā)生缺陷(陷阱、電荷)的積累�,積累的缺陷達(dá)到某一程度后,使局部區(qū)域的電場(或缺陷數(shù))達(dá)到某一臨界值��,轉(zhuǎn)入下一階段:

2)第二階段是在熱��、電正反饋?zhàn)饔孟?�,迅速使氧化層擊穿的過程���。柵氧壽命主要由第一階段中的建立時間所決定��。對電應(yīng)力下氧化層中及界面處產(chǎn)生的缺陷���,一般多認(rèn)為是電荷引起的,對電荷的性質(zhì)�����,主要有二種理論模型:負(fù)電荷積累模型和正電荷積累模型(此處不作詳細(xì)說明)���。

(2) 柵氧化物愈合/短路

形成的絲狀鋁硅合金也可能在后續(xù)的靜電放電作用下被燒毀�����,從而使氧化柵得到“自愈”��。但“自愈”的氧化柵會由于不可靠而降級����,它會在后續(xù)的工作中遇到過應(yīng)力或是低能量的ESD脈沖時�����,容易使缺陷擴(kuò)大或使氧化柵發(fā)生短路���。

(3) 內(nèi)部保護(hù)電路受損

集成電路內(nèi)部通常設(shè)計(jì)了ESD保護(hù)電路��。常見的CMOS器件內(nèi)部電應(yīng)力保護(hù)電路單元有:電阻����、二極管���、MOS管���、SCR等。器件內(nèi)部的電應(yīng)力保護(hù)網(wǎng)絡(luò)通常由這幾個保護(hù)電路單元的一種或者多種組合構(gòu)成����,具體的選擇應(yīng)根據(jù)電路參數(shù)��、工藝類型和版圖設(shè)計(jì)的實(shí)際情況決定�。

圖4. 器件內(nèi)部的ESD保護(hù)電路

當(dāng)起保護(hù)作用的二極管受到破壞��,其I-V特性曲線變壞�����,在電流的傳輸過程中產(chǎn)生時間延遲效應(yīng)��,波形的時間延遲會使器件產(chǎn)生細(xì)微的損傷���。

(4) 電荷陷阱

靜電放電產(chǎn)生的高壓瞬時脈沖會破壞器件上的電荷平衡�����,從而形成電荷陷阱���。大量的電荷積聚在器件表面形成反型層,該反型層提供了電流泄漏通路���,反型層泄漏是一個與時間和溫度有關(guān)的退化現(xiàn)象��,它會導(dǎo)致器件完全失效�����。

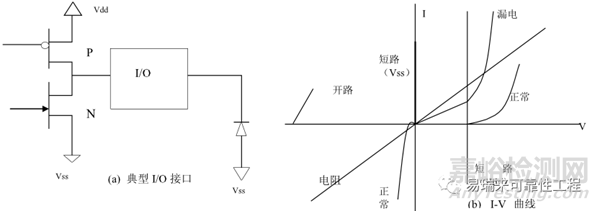

(5) PN結(jié)衰減

通過觀察硅PN結(jié)的I-V特性曲線就可以發(fā)現(xiàn)它是否已經(jīng)損傷��。瞬時的局部加熱或電應(yīng)力都會使鋁硅合金絲狀化��,這些絲狀物構(gòu)成了一個并行分流器�����,在反偏I(xiàn)-V特性曲線上形成一個尖銳的拐點(diǎn)��。鋁硅合金熔融需要很高的溫度��。在ESD引起損傷的事件中���,PN結(jié)絲狀橫截面積變得很小,以至于在使用過程中產(chǎn)生局部加熱��,從而導(dǎo)致失效�。靜電放電熔斷如此小的細(xì)絲是非常可能的,從而使器件雖然可以使用但卻不再可靠�����。

圖5. 典型I/O電路及其I-V曲線

二���、半導(dǎo)體的ESD失效機(jī)理

半導(dǎo)體器件的靜電損傷����,其失效機(jī)理可分為兩類:一類是與電流有關(guān)的失效�����,如PN結(jié)的損傷�����,接觸孔合金釘����,金屬/多晶硅互連線或電阻燒壞;另一類是與電壓有關(guān)的失效��,ESD引起柵氧化層擊穿是最常見的電壓型失效��。

2.1電流型損傷機(jī)理

(1) PN結(jié)的損傷和接觸孔合金釘

ESD引起PN結(jié)短路是最常見的失效現(xiàn)象。當(dāng)PN結(jié)(尤其是淺PN結(jié)�����,如雙極型晶體管的發(fā)射結(jié)或NMOS管的漏極與襯底間的結(jié))發(fā)生雪崩擊穿�����,再進(jìn)一步發(fā)展為二次擊穿時����,瞬態(tài)大電流產(chǎn)生的焦耳熱導(dǎo)致局部溫度急劇上升��,這一局部的熱量 又會加速熱載流子的產(chǎn)生���,大量產(chǎn)生的熱載流子又會進(jìn)步增大瞬態(tài)大電流�����, 最后導(dǎo)致局部溫度超過1415攝氏度而發(fā)生硅的熔化��,引起合金釘穿透PN結(jié)而失效�。如果產(chǎn)生的熱量足夠熔化鄰近接觸孔的金屬�,熔化的金屬會在電場的作用下在結(jié)間遷移,導(dǎo)致結(jié)間的電阻型短路。當(dāng)位于PN結(jié)二次擊穿點(diǎn)處的熔化的硅發(fā)生再凝固時�����,PN結(jié)處的P型和N型摻雜劑的分布發(fā)生了改變�����。而且��,再分布的過程改變了硅的晶體性質(zhì)��。這些變化導(dǎo)致結(jié)間反向漏電流小幅或大幅增加����。版圖設(shè)計(jì)對PN結(jié)短路有很大影響,最敏感的是接觸孔尺寸���、形狀及位置���。較好的辦法是在一個擴(kuò)散區(qū)內(nèi)設(shè)置多個小接觸孔,以便增加孔周長:用圓形接觸孔可避免電流的非均勻流動:增加接觸孔與擴(kuò)散區(qū)的間距��,可防止電流在接觸孔角落處集中�����。

(2) 金屬/多晶硅互連線或電阻燒壞

ESD事件產(chǎn)生的局部焦耳熱也可能使金屬/多晶硅互連線或電阻燒壞,這主要取決于鋁線或多晶硅線的寬度��、接觸孔尺寸�、結(jié)面積和電流分布等?���;ミB線的電流攜帶能力是它的橫截面積的函數(shù),并且還與電流聚集�����、臺階覆蓋和熱阱等因數(shù)有關(guān)�。例如由于氧化層臺階處的鋁層橫截面積的減小�����,在ESD脈沖的大電流作用下���,鋁層更容易熔化而開路��,導(dǎo)致器件的功能失效����。ESD脈沖大電流有時只是部分熔化電阻材料,導(dǎo)致電阻值的漂移和相關(guān)器件電參數(shù)的失效���。當(dāng)輸入ESD保護(hù)電路中有多晶硅電阻時��,靜電放電容易使多晶硅電阻受到損傷��,失效部位常出現(xiàn)于多晶硅電阻拐彎處和多晶硅電阻與鋁互連線的接觸孔處�。擴(kuò)散電阻的抗靜電能力明顯好于多晶硅電阻��,這是因?yàn)閿U(kuò)散電阻的襯底可充當(dāng)為一個有效的熱阱�����,而多晶硅電阻周圍的介質(zhì)氧化層卻阻礙了多晶硅電阻的散熱�����?�;ミB線承受大電流能力依賴它的橫截面積���,因此輸入保護(hù)結(jié)構(gòu)應(yīng)盡量靠近鍵合焊盤(PAD)以縮短鋁互連線長度���,鋁互連走線應(yīng)做得足夠?qū)?��,以提高抗電過應(yīng)力的能力。電阻抗電過應(yīng)力的的能力取決于其端頭�����、接觸孔的大小以及電阻條寬與長度���。

2.2電壓型損傷機(jī)理

(1) 柵氧化層損傷

當(dāng)半導(dǎo)體器件遭受極短上升時間的ESD脈沖時(如帶電器件模型)�����,ESD保護(hù)器件還未作出及時反應(yīng)�����,ESD 電壓就直接加到處在ESD保護(hù)器件下一級的MOS器件的柵極上,導(dǎo)致柵氧化層損傷��。柵氧化層擊穿是最常見的過電壓場致失效��。過高的ESD電壓可能使介質(zhì)層損傷����,其損傷過程可分成以下三個階段���。首先,在介質(zhì)層的某個高電場點(diǎn)(如介質(zhì)層的邊角和臺階處)���,ESD脈沖產(chǎn)生的高壓超過了介質(zhì)的絕緣強(qiáng)度�����;其次���,介質(zhì)擊穿形成的大電流流過擊穿點(diǎn),產(chǎn)生相鄰區(qū)域的熱斑����;最后,局部的高溫熔化了多晶硅柵����,形成多晶硅熔化絲狀物,或者��,當(dāng)柵氧化層由于制造工藝缺陷而有針孔時����,ESD電壓會使得擊穿首先在針孔處發(fā)生���。

(2) 鋁互連線與擴(kuò)散區(qū)短路

短路常發(fā)生在鍵合焊盤(PAD)連接的擴(kuò)散電阻和橫跨其上的電源鋁條之間。由于它們之間是熱氧化層且厚度較厚���,所以這種短路失效幾率比較小��。

(3) 鋁互連線與多晶電阻短路

短路常發(fā)生在鍵合焊盤(PAD)連接的多晶電阻和橫跨其上的電源或地互連線之間�����。由于鋁互連線與多晶硅電阻之間介質(zhì)擊穿強(qiáng)度比熱氧化層低得多�����,當(dāng)輸入端引入ESD時可導(dǎo)致該處介質(zhì)擊穿短路�,因此版圖設(shè)計(jì)時輸入端的多晶硅電阻條與鋁條之間應(yīng)留足夠距離��,更要防止多晶硅電阻條與鋁條重疊���。

三、如何防范ESD對半導(dǎo)體的損傷

解決問題的不二法則�����,一方面加強(qiáng)自身的防護(hù)能力(內(nèi)因);另一方面管控靜電產(chǎn)生�����、積累和泄放的所有場景(外因)���。

因此,在設(shè)計(jì)芯片時必須提升芯片自身的ESD防護(hù)能力���,尤其對于外部接口類器件��。但隨著集成電路的集成度越來越高����,在芯片內(nèi)部設(shè)計(jì)防護(hù)電路的成本也越來越高�����,甚至由于半導(dǎo)體工藝限制和信號特性的要求�,難以在芯片內(nèi)部增加防護(hù)電路,這就要求在使用芯片進(jìn)行應(yīng)用電路設(shè)計(jì)時,一定要充分考慮元器件��、電路板���、整機(jī)的ESD防護(hù)����。

另外����,從芯片本身的半導(dǎo)體制程中以及電路板PCBA的全生產(chǎn)過程中務(wù)必加強(qiáng)從人、機(jī)��、料�����、法�����、環(huán)等各個方面對ESD進(jìn)行管控�,減少靜電來源,并使靜電能以安全方式和通路泄放掉����,不會直接作用到器件引腳上。