Wafer-to-wafer hybrid bonding

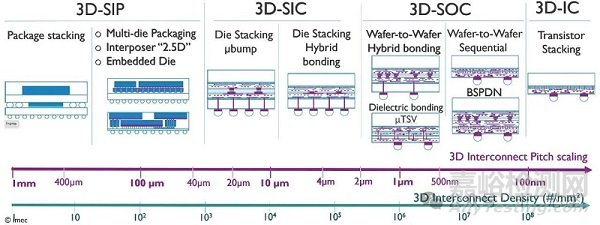

3D集成是實現(xiàn)“多芯片異構集成”的關鍵技術��,也是產業(yè)界對系統(tǒng)級“功耗-性能-面積-成本”持續(xù)增益需求的回應����。3D堆疊正被引入電子系統(tǒng)層級的各個階段,從封裝級一直下沉到晶體管級����。為此,多年來已衍生出多種3D互連技術��,其互連節(jié)距從毫米級到<100 nm�,覆蓋不同應用需求��。下圖為這一“3D互連版圖”的示意����,該版圖高度動態(tài),每種技術都在不斷縮小節(jié)距。位于版圖最右端的是晶圓對晶圓混合鍵合(wafer-to-wafer hybrid bonding)��,它承諾超高互連密度與極低互連寄生�。該“混合”方案同時實現(xiàn)Cu-Cu金屬鍵合與介電-介電鍵合,采用Cu大馬士革工藝定義鍵合面�,具備向更細節(jié)距擴展的潛力。

Fig.1: The imec 3D interconnect technology landscape.

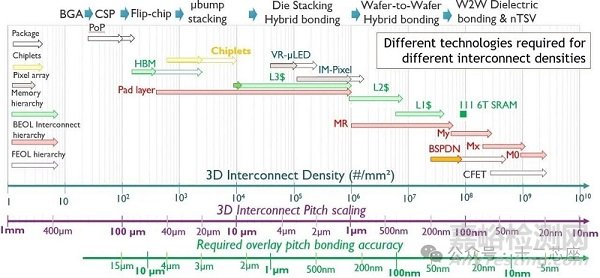

直到最近�,wafer-to-wafer hybrid bonding 的大規(guī)模量產仍主要局限于“圖像傳感器堆疊在信號處理電路上”這一領域。如今�,該技術開始被用于在3D NAND頂層集成CMOS外圍電路。這些商業(yè)應用充分利用了混合鍵合“每平方毫米可集成百萬級互連”的能力��,其關鍵是Cu互連節(jié)距已微縮至約1 µm�。另一大優(yōu)勢在于,它能“混搭”不同材料�、不同功能以及不同世代的CMOS工藝。

Fig.2: Imec’s 3D interconnect technology scaling roadmap

未來幾年����,預計其應用范圍將大幅擴張。借助系統(tǒng)-技術協(xié)同優(yōu)化(STCO)����,電路劃分將下沉到更低的設計層級——可細化至功能模塊甚至標準單元層面。我們已經看到首批“存儲器上邏輯”(memory-on-logic)方案的發(fā)布�,例如SRAM直接堆疊于邏輯芯片之上��,這成為推動先進晶圓對晶圓混合鍵合發(fā)展的主要動力之一����。要充分釋放其潛力����,研究人員必須將互連節(jié)距進一步縮至遠小于1 µm。

Hybrid bonding 工藝流程

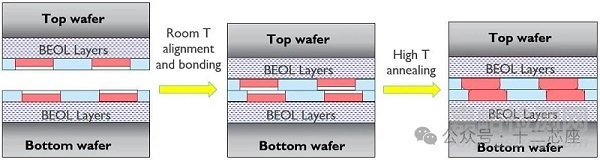

Fig.3: The classical wafer-to-wafer hybrid bonding process flow.

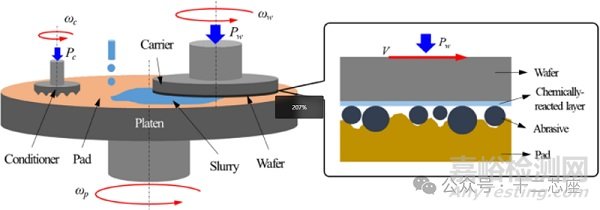

如今的混合鍵合從兩張已完成功能前端(FEOL)與多層后端(BEOL)的300 mm晶圓開始�。前半段類似片上BEOL大馬士革工藝:在鍵合介電層(通常為SiO?)上刻出微腔,依次沉積阻擋層�、種子層與Cu,再進行化學機械拋光(CMP)��。該CMP需達到整片納米級均勻度����,使介電表面極致平坦,同時讓Cu盤略陷數(shù)納米��。經高精度對準后��,兩晶圓在室溫下自中心點接觸�,表面吸附產生“鍵合波”��,由中心向邊緣迅速閉合縫隙。隨后升溫退火��,完成介電-介電與Cu-Cu的永久鍵合�。

挑戰(zhàn)

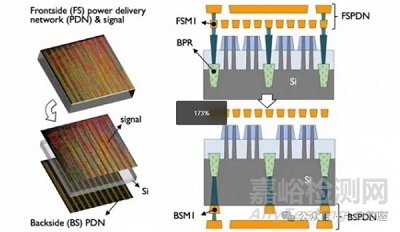

隨著應用范圍向“前端附近”拓展(如邏輯-on-邏輯、存儲器-on-邏輯)����,鍵合節(jié)距需進一步縮小,且鍵合后仍需大量加工��。

典型例子是背面供電網絡(BSPDN):首片晶圓正面先與承載片鍵合��,隨后將其背面磨薄�,完成n-TSV刻蝕、金屬填充與背面金屬化�,即部分“最粗”供電互連要在鍵合后才形成。這類場景對現(xiàn)有流程提出更嚴苛的縮放要求:Cu-Cu對準精度����、鍵合前晶圓潔凈度與形貌、微節(jié)距下介電與Cu盤的鍵合強度����,均成為主要瓶頸。

Hybrid bonding improve

在2023年國際電子器件會議(IEEE IEDM 2023)上����,imec報告了重要的創(chuàng)新成果�,為實現(xiàn)前所未有的400納米互連間距鋪平了道路�。這些成果來自于一項全面的研究,該研究考察了晶圓對晶圓混合鍵合的各個方面����。

為補償縮小和對準限制而進行的設計改進。imec的研究人員首次提出了一種測試載體設計��,采用六邊形網格和圓形銅(Cu)焊盤����,而不是傳統(tǒng)的正方形網格以及正方形或圓形焊盤設計。這種新設計具有多項優(yōu)勢��。它可以以最密集的方式排列銅焊盤�,使所有相鄰焊盤之間的距離相等。因此�,在進一步縮小尺寸時,這種配置更容易控制銅焊盤密度�,同時最大化銅焊盤的尺寸和間距。該團隊還在研究使用等墊設計或不等墊設計的影響�。在后一種情況下,上層晶圓的銅焊盤關鍵尺寸比下層晶圓小��。不等墊設計具有幾項優(yōu)勢����,包括更大的鍵合對準容差、更小的寄生電容以及在小互連間距下更高的介質擊穿強度����。

CMP

在兩片晶圓鍵合之前,兩片晶圓的表面必須極其平整且干凈��,才能實現(xiàn)可靠的混合鍵合工藝�。因此,化學機械拋光(CMP)是一個非常關鍵的工藝步驟����。它還確保銅焊盤的均勻凹陷,即在鍵合之前�,銅保持在介質表面以下幾納米。這是為了在退火后實現(xiàn)無空洞鍵合�。通過將先進的CMP工藝與布局設計中的虛擬焊盤相結合,研究人員成功地在整個晶圓上精確控制了銅焊盤的高度和表面形貌�。

SiCN介質

imec此前曾提議將SiCN作為小互連間距的首選介質。與SiO?表面相比�,SiCN表面展現(xiàn)出更高的鍵合能量——這意味著需要更多的能量才能打破鍵合。此外����,SiCN作為銅的擴散勢壘和晶圓鈍化層�,能夠阻擋氣體擴散����,從而實現(xiàn)更熱穩(wěn)定的鍵合界面。這些特性在縮小混合鍵合互連間距時變得越來越重要�。基于納米壓痕法——一種新興的鍵合強度評估技術——的測量結果證實�,SiCN-SiCN鍵合強度顯著優(yōu)于SiO?-SiO?鍵合強度。在僅250°C的后鍵合退火后即可獲得高鍵合強度����,并且在更高溫度下不會退化。

400nm間距互連

利用上述見解�,研究人員進行了先進的晶圓對晶圓銅/SiCN鍵合工藝。實際鍵合是使用一臺配備先進對準功能的商用高質量晶圓鍵合設備完成的——這種設備對于工藝的成功至關重要�。成功鍵合了300毫米晶圓,實現(xiàn)了具有前所未有的400nm間距的銅互連��。

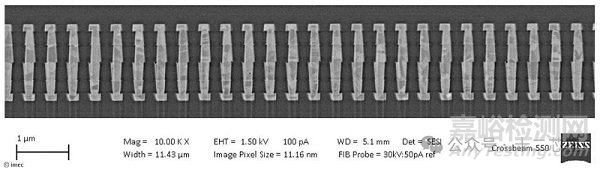

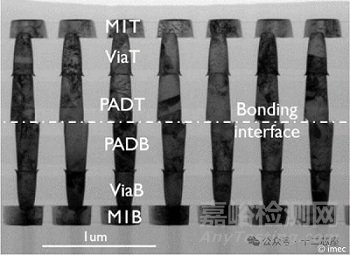

Fig.4: TEM image showing multiple Cu pads connected at 400nm pitch (equal pad design).

Fig.5: Zoom in on 400nm pitch long daisy chains in equal pad design, used to evaluate the Cu-Cu connectivity(IEDM)

結果表明成功控制了銅/硅碳氮化物(SiCN)表面形貌��,實現(xiàn)了精確對準(對準精度低于150納米)����,并且具有良好的電氣性能(即單個接觸電阻低)�。

對準精度的需求

團隊首次研究了鍵合對準精度與可靠性(即介質擊穿和產量)之間的關系�。結果證實,在小互連間距下�,不等墊設計的銅焊盤比等墊設計的銅焊盤具有更高的介質擊穿強度。團隊還得出結論����,對于這些400納米的互連間距�,為了在大批量制造中獲得足夠的產量,對準精度需要小于100納米�。因此,滿足未來三維系統(tǒng)級芯片(3D-SOC)設計的需求�,對下一代晶圓鍵合設備的對準精度提出了極高的要求。

結論

晶圓對晶圓混合鍵合作為一種有前景的三維集成技術��,能夠實現(xiàn)不斷增加的輸入/輸出(I/O)密度和功能芯片之間更高效的連接����。為了實現(xiàn)像邏輯芯片上的存儲器這樣的應用——在這種應用中,wafer to wafer 鍵合發(fā)生在前端附近——銅互連間距的縮小必須達到極限��。改進網格設計��、增強表面形貌控制����、使用硅碳氮化物作為介質��、對鍵合機制的基本理解以及對準精度的提高被確定為實現(xiàn)400納米(及以下)間距下電氣功能和可靠的銅互連的關鍵推動力����。這些結果為開發(fā)具有更小互連間距的未來晶圓對晶圓鍵合工藝奠定了基礎��。