背景

電磁干擾 (EMI) 是外部源對電路造成的不利干擾。EMI可以分為傳導(dǎo)或輻射��。傳導(dǎo)EMI 是由寄生阻抗����、電源和接地連接引起的一種傳導(dǎo)耦合����。輻射 EMI 是來自無線電傳輸?shù)臒o用信號的耦合��。本文主要討論了如何通過頻率規(guī)劃和印刷電路板 (PCB) 設(shè)計盡量減少時鐘器件產(chǎn)生的輻射 EMI。

在為 EMI 敏感應(yīng)用設(shè)計PCB 布局時�����,最好實施一種經(jīng)過優(yōu)化的初步設(shè)計,以實現(xiàn)最佳 EMI 性能�����。本文討論了這些布局策略以及如何充分利用時鐘信號特性來實現(xiàn)最佳 EMI 性能����。

輸出建議

1. 差分與單端

時鐘波形往往具有非常高的轉(zhuǎn)換率。無論是在輸出頻率還是在后續(xù)諧波中��,這種劇烈的電壓變化都容易導(dǎo)致較大的 EMI 尖峰��。例如�����,25MHz 可能在 25MHz��、50MHz(第 2 個諧波)、75MHz(第 3 個諧波)處產(chǎn)生EMI 雜散��,以此類推����。在生成這些輸出的同時諧波是無法避免的,因此�����,選擇正確的輸出類型有助于降低雜散的功耗����。

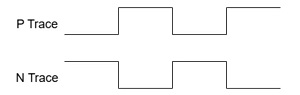

使用差分輸出類型(例如 LVDS 或 HCSL)就是最佳狀況�����。差分信號同時使用 P 布線和 N 布線,每條布線的相位差為 180 度�����。當(dāng)P 為高電平時����,N 為低電平��,反之亦然 (圖1)。此外�����,從時鐘發(fā)生器到終端器件之間�����,差分信號在整個 PCB 上的布線非?����?拷_@種模式和較短的距離能有效地將單條布線的 EMI 影響降至最低��。

圖1. P 和N 布線

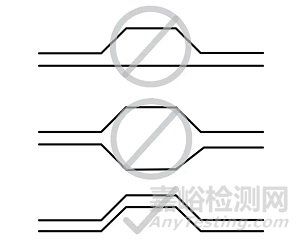

我們可以將相同的方法用于單端輸出類型��,例如 CMOS。與差分信號不同�����,單端輸出類型沒有相同的 P 和 N 關(guān)系����;通常僅使用P 布線或 N 布線��。但是許多時鐘器件可以通過單個輸出通道塊產(chǎn)生兩個彼此相位差為 180 度的單端信號。我們可以通過盡可能接近的模擬差分信號��,讓這一點給我們帶來益處。按照差分對布線可實現(xiàn)出色的 EMI 性能����。如果僅使用 LVCMOS 對的其中一條,則進(jìn)行兩條布線��,盡可能靠近接收器終止不使用的一條布線�����。如果 LVCMOS 對用于兩個不同的接收器��,請制定頻率計劃和 PCB 布局�����,以便盡可能按照差分方式對時鐘對進(jìn)行布線。

圖2. 差分對對稱

使用 CMOS 時����,考慮布線長度也很重要。這種輸出類型的布線越長��,需要的功率就越大��,繼而產(chǎn)生更大的 EMI輸出雜散�����。無論是差分輸出還是單端輸出��,最好盡可能使用低功耗輸出類型��,例如��,使用 LVCMOS 而不是CMOS����,或使用LP-HCSL 而不是 HCSL。

2. 壓擺率

轉(zhuǎn)換率是指電壓電平的變化率��。時鐘信號通常是方波�����,與其他類型的信號相比��,轉(zhuǎn)換率通常更快����。電壓電平快速變化,導(dǎo)致電路中出現(xiàn)電流浪涌�����,從而產(chǎn)生 EMI 尖峰��。為了減輕這種影響��,CDC6C 之類器件采用了轉(zhuǎn)換率控制(也稱為可調(diào)節(jié)上升或下降時間)��。降低轉(zhuǎn)換率可減少電流浪涌��,從而降低功耗 EMI 尖峰��。

3. 擴頻時鐘

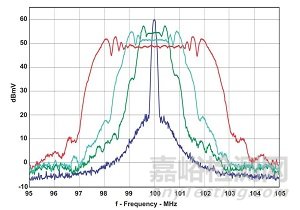

展頻時鐘 (SSC) 是緩解這種 EMI 來源的最常用策略����。SSC能夠通過以受控方式改變頻率來降低數(shù)字時鐘信號的峰值振幅,從而將能量分散在頻域中。然而��,這不會影響時域中的時鐘振幅��。中心展頻 SSC 將能量均勻分散在目標(biāo)頻率的任一側(cè)�����。向下展頻 SSC 僅將能量分散到目標(biāo)頻率以下的頻率��。兩種 SSC 強度可能會有所不同�����。圖3顯示了0 %(藍(lán)色)�����、±0.5%(綠色)��、±1%(青色)和±2%(紅色)中心展 SSC 的結(jié)果����。

3. 100MHz 輸出,具有 0%��、 ±0.5%、 ±1% 和±2 % SSC

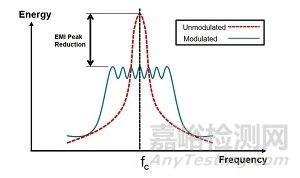

展頻通過將窄帶信號轉(zhuǎn)換為寬帶信號�����,以將能量分散在多個頻率上����,從而降低 EMI 的影響�����。在開關(guān)穩(wěn)壓器中�����,振蕩器設(shè)置的開關(guān)頻率在操作下可降低峰值能量����,并分布到其他頻率及其諧波。圖4說明了隨時間操作時鐘頻率如何分散開關(guān)電源生成的能量�����。

圖4. 展頻頻率調(diào)制降低EMI

有多種方法可實現(xiàn)展頻����;也可通過不同的技術(shù)來實現(xiàn)����,例如三角模擬抖動����、假隨機、自適應(yīng)隨機展頻 (ARSS)�����、雙隨機展頻 (DRSS) 及許多其他技術(shù)�����。其中每種技術(shù)通常在低頻率或高頻率下更有效����。請注意,EMI 總能量沒有變化�����,因為沒有衰減�����。而展頻技術(shù)會改變傳導(dǎo)和輻射干擾功率譜的形狀�����,從而降低峰值發(fā)射水平��。

PCB 設(shè)計

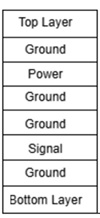

1. 堆疊

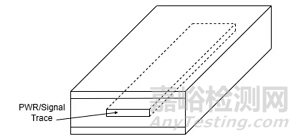

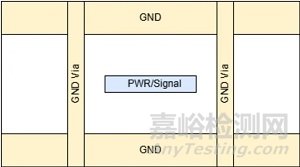

為了最大限度降低 EMI����,請規(guī)劃PCB 堆疊��,使時鐘信號和電源布線采用帶狀線 (圖5)��。使用接地環(huán)繞這些高能源有助于進(jìn)行現(xiàn)場抑制����。圖5 顯示了一個 8 層堆疊的示例。該示例使用第 1 層��、第3 層和第 6 層進(jìn)行電源和信號布線,并用接地平面環(huán)繞其中每一層����。雖然僅使用這種堆疊并不能完全包覆住布線����,但的確可以覆蓋大部分表面區(qū)域�����,有助于限制輻射EMI�����。

圖5. 展頻頻率調(diào)制降低EMI

圖6. 8 層PCB 堆疊示例

除了層順序外����,還必須考慮材料特性對布線阻抗的影響�����。布線寬度和堆層疊必須確保和所用輸出類型的布線進(jìn)行正確的阻抗匹配��。例如,LVCMOS 通常需要 50Ω 布線阻抗�����,而 LP-HCSL 通常使用 85Ω 或100Ω。當(dāng)器件和信號層未實現(xiàn)阻抗匹配時�����,其過渡可能會導(dǎo)致較大的 EMI 雜散����。大多數(shù) PCB 軟件和制造商都提供工具,可以協(xié)助完成此過程����。如果使用過孔將時鐘布線走線到不同的層�����,還必須要考慮過孔阻抗。

2. 電源濾波

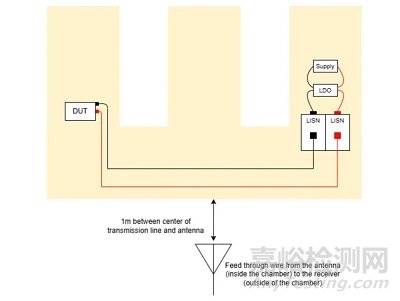

頻率在電源平面上耦合和輻射,是一種常見 EMI 來源����。如果需要 CISPR-25 認(rèn)證,這一點尤為重要�����,因為天線測量是通過器件的電源線進(jìn)行的 (圖7)��。

圖7. CISPR-25 設(shè)置

使用去耦電容器是在電路中產(chǎn)生純凈電源的主要方法����。電容器在連接到直流電源后存儲能量��,因此如果電壓從標(biāo)稱值波動��,電容器內(nèi)存儲的能量會釋放并輸送到負(fù)載����。這會拉平總電壓,保持電源穩(wěn)定并減少 EMI 雜散�����。

去耦電容器的常見值為 0.1uF 和 1uF����;但是,這些值無法濾除每個頻率��。電容器的內(nèi)部電阻有限��,且具有電阻和電感特性�����。發(fā)生諧振以及容抗和感抗相等的頻率稱為自諧振頻率 (SRF)����。在該頻率處,電容器阻抗變?yōu)榱?���。在我們希望對電源進(jìn)行濾波的頻率處,我們需要去耦電容器的阻抗盡可能低�����。

3. 避免產(chǎn)生瓶頸

如上一節(jié)所述����,電源平面和接地平面可以作為強大的 EMI 輻射源。PCB 設(shè)計中的一個常見錯誤是在電源和接地布線中造成瓶頸����。當(dāng)功耗大量強制集中在一個較小的區(qū)域時�����,就會出現(xiàn)瓶頸����。

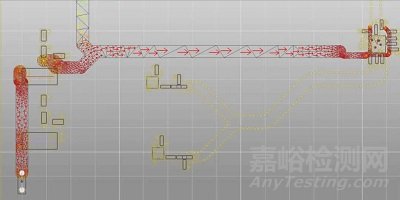

在以下各圖中��,紅色箭頭表示較大的功耗集中��,綠色箭頭表示較小的功耗集中�����。

在圖8 中��,VDD 布線變?yōu)檩^窄的布線��。其中��,兩處連接是瓶頸��。該區(qū)域大量集中了電流��,可充當(dāng) EMI 天線����,如紅色箭頭所示

圖8. 窄電源布線

在新布局中(圖9),利用的是整個平面而不是單條布線�����,這降低了任何給定點的功率集中�����,如綠色箭頭所示����。

圖9. 更寬的電源布線

4. 戰(zhàn)略性過孔布置

4.1 分散功耗集中

任何大量功耗集中都可能導(dǎo)致 EMI 雜散。雖然節(jié) 3 中討論了功耗集中和布線寬度��,但 PCB 的其他區(qū)域也會出現(xiàn)大量功耗集中的情況��。過孔和無源器件在連接點往往具有這類更高程度的功耗集中�����。例如����,如果過孔明顯小于布線寬度��,這種過渡可以充當(dāng) EMI 天線����。同樣�����,較大的無源元件焊盤連接到寬度較小的布線或兩個平面之間的過渡�����,可能具有相同的效果��。

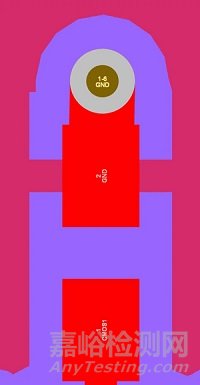

穿過過孔布線會造成電流干擾��,可能導(dǎo)致 EMI 尖峰����。然而,如果過孔明顯大于布線寬度��,則會產(chǎn)生更突兀的過渡(圖10)�����。這種更突兀的過渡可以充當(dāng)天線����,產(chǎn)生更大的 EMI 雜散。穿過過孔布線時����,布線寬度應(yīng)略大于過孔(圖11)����。

圖10. 采用窄布線穿過接地過孔的無源器件

圖11. 采用較寬布線穿過接地過孔的無源器件

較大的無源元件焊盤連接到寬度較小的布線,也可以是 EMI 尖峰的來源 (圖12)����。連接無源器件時,布線寬度要與焊盤尺寸相匹配�����。同樣����,在兩個平面之間連接網(wǎng)時�����,使用幾個過孔更均勻地分散能量 (圖13)����。這對于電源網(wǎng)和接地網(wǎng)尤其重要�����。

圖13. 大型無源器件和較少的過孔

圖14.大型無源器件和很多過孔

4.2 屏蔽和拼接過孔

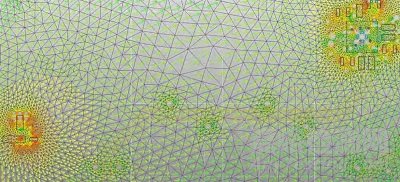

在 PCB 設(shè)計中����,降低 EMI 的常用方法是使用穿孔拼接和屏蔽過孔。拼接是指使用散布在整個電路板上的通用接地過孔模式��。根據(jù)設(shè)計需求�����,每個過孔之間的間距可以變化��。這些過孔將 PCB 的接地平面連接在一起����,為電路形成一個穩(wěn)固的整體接地�����。額外的接地還用于進(jìn)一步環(huán)繞電源平面或布線��,有助于現(xiàn)場抑制 (圖15)�����。在電路中提供穩(wěn)固的接地是降低 EMI 的最有效方法之一。

圖15. 利用過孔實現(xiàn)帶狀線堆疊

妥善做法是在連接點布置一個額外的接地過孔 (圖16)��。連接點可以是布線連接到另一元件的任何位置�����,例如過孔或無源器件��。額外的過孔可實現(xiàn)更短的接地路徑����,減少電感和 EMI����。

圖16. 帶有接地過孔的電阻器(靠近布線連接點)

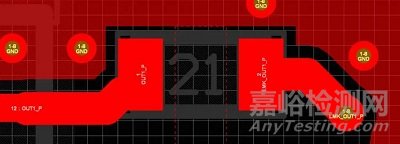

屏蔽也利用接地過孔。但是��,屏蔽過孔不會散布在整個電路板上����,而是沿信號布線布置 (圖17)。這些過孔可以幫助濾除某些頻率��。對于較低的時鐘頻率��,以波長的 1/20 將一組過孔隔開��;對于較高頻率��,以波長的1/10 將其隔開����。雖然這種方法優(yōu)先處理帶狀線相關(guān)的布線,但使用通孔過孔可能和使用拼接過孔有著類似的效果�����,可以加強電源平面的整體接地和帶狀線部分��。

圖17. 帶有屏蔽過孔的時鐘布線

盡量減少可能使用的天線數(shù)量

1. 殘樁

電路中的任何殘樁都可能成為天線,而 PCB 表面的殘樁在頂部沒有額外接地層來實現(xiàn)場抑制��。元件焊盤(尤其是DNP 焊盤)是常見的殘樁示例����。最好在頂層實施接地覆銅以環(huán)繞元件周圍并將接地平面作為第二層來減少影響。

2. 網(wǎng)絡(luò)覆銅

在PCB 頂層形成接地覆銅時��,自動化軟件有時可以在元件之間形成接地手指(圖18)����。這些手指可以通過切斷接地覆銅清除 (圖19)。

圖18. 接地手指

圖19. 接地手指已清除

同樣��,檢查網(wǎng)絡(luò)覆銅的邊界是否平滑����。覆銅中存在的任何毛刺都會導(dǎo)致電流阻滯和輻射����。

圖20. 帶有毛刺的電源覆銅

總結(jié)

PCB布局是影響系統(tǒng) EMI 性能的主要因素之一。在設(shè)計電路板時�����,它是(通過電容器和鐵氧體磁珠)保持純凈電源并(通過額外的接地過孔)維持穩(wěn)固接地的關(guān)鍵。PCB 層堆疊和布線布局也可以進(jìn)行優(yōu)化�����,以提供額外的接地屏蔽和平滑的功率流��?���?梢允褂貌煌脑O(shè)置(如 SSC)進(jìn)一步降低 EMI 發(fā)射。