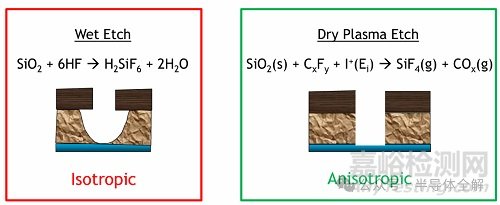

晶體管溝道制備需要刻蝕硅材料�,常用的辦法有干法和濕法兩大類,濕法刻蝕通常難以實現(xiàn)高分辨率�。目前基于反應離子刻蝕設備的干法刻蝕方法已經(jīng)相當成熟。

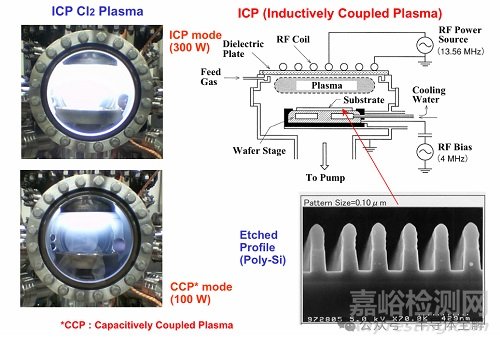

常用的設備是RIE和ICP-RIE���,可以更好地控制等離子體密度和能量�,實現(xiàn)高深寬比�����、高精度的納米級三維結構加工。

反應離子刻蝕速度較快�����,主要原因是它不僅有物理轟擊的刻蝕效果�,而且可以選擇特定氣體使其產(chǎn)生的等離子體與待刻蝕材料發(fā)生化學反應達到高效的刻蝕目的。

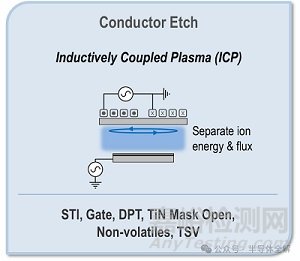

ICP-RIE相較于RIE���,其頂部增加一個射頻功率源(ICP源)�,通過感應線圈的方式將此射頻功率源耦合進入設備腔體�����,從而將等離子體的產(chǎn)生與刻蝕兩個步驟分開���。

頂部的感應線圈 使得等離子體在墻體頂部做高速回旋運動,充分接觸氣體實現(xiàn)完全電離�。

在樣品臺基板上的射頻源(RIE源)則可以設定指定功率,完成對垂直方向的自偏置電壓控制���。

ICP-RIE與RIE相比較具備高等離子體密度�、可控的等離子體能量兩點優(yōu)勢�����,使其擁有高刻蝕選擇比���、高刻蝕速率等優(yōu)點���,在加工高深寬比、高精度的結構中大有作為�����。

目前常見的刻蝕硅的氣體有C4F8/SF6�����,CF4/SF6�,SF6/O2,HBr�,SiCl4/Cl2 等。

在這些刻蝕方法中�,博世(Bosch)工藝、準博世(Pseudo Bosch)工藝�、低溫工藝���、HBr 工藝較為常見。

下來我們主要介紹的工藝為低溫和 Pseudo Bosch 工藝�����。

二���、Si溝道低溫刻蝕工藝

低溫刻蝕硅的工藝�����,首次由Tachi等人提出���,其反應氣體是SF6和O2�����,襯底溫度范圍為-85℃到-140℃���。

低溫刻蝕工藝最大的優(yōu)點便是可以克服 Bosch 工藝產(chǎn)生的“波紋”效應。

在低溫刻蝕過程中���,SF6為蝕刻氣體,O2為鈍化氣體���。

SF6在等離子體中被電離���,產(chǎn)生F-、SFx 等活性強的等離子基團���,其中起主要刻蝕作用的是F -�。

F-與樣品上的Si接觸并發(fā)生化學反應���,產(chǎn)生一種揮發(fā)性氣體SiF4�����,蝕刻產(chǎn)物被分子泵從腔 體中抽出�。與此同時���,在低溫條件下���,Si與F-和O-發(fā)生反應產(chǎn)生的副產(chǎn)物SiOxFx 會部分冷凝在Si結構表面���,形成一層保護層,防止F-進一步與Si反應�����,從而避免了F-對 Si 的橫向刻蝕�����。而在垂直方向由于存在等離子體物理轟擊過程���,很難形成有效的鈍化層,從而實現(xiàn)高深寬比的Si三維結構加工�。

刻蝕的基本參數(shù)對蝕刻速率和蝕刻結構的形貌有重大影響。

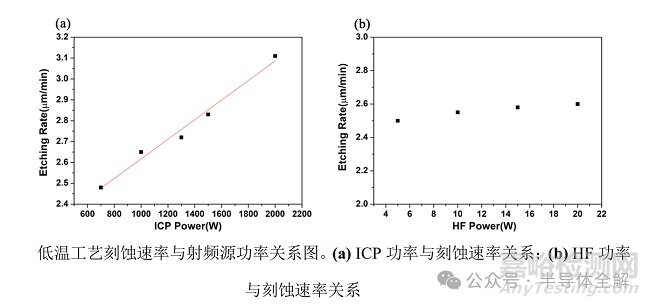

如前所述���,使用ICP-RIE 的優(yōu)點是可以將等離子體的產(chǎn)生與刻蝕兩個步驟分開���。低溫蝕刻工藝主要是活性等離子體與襯底材料的化學反應,因此控制產(chǎn)生的F-密度可以極大影響 蝕刻速率�����?����?梢酝ㄟ^ICP功率���、SF6氣體流量和腔體反應壓力來控制所產(chǎn)生的F-密度�。

增加ICP功率本質上就是使同等腔體內的SF6分子電離的更充分�,以此達到增加F-密度。

如上圖(a)所示�����,隨著 ICP 功率的增加���,蝕刻速率也隨之基本呈現(xiàn)線性增加���。

除此之外,增大氣體流量也可以提高等離子體密度�����,但氣體流速超過特定值之后,刻蝕速率反而降低���,這主要是由于過高的氣體流速使得離子散射增加���,等離子體密度降低。

增加反應氣壓也可以使刻蝕速率得以增加���,但氣體流量不變的情況下會使得等離子體不穩(wěn)定�����,其刻蝕速率難以控制���。

由于低溫刻蝕工藝主要是化學刻蝕,垂直方向射頻源HF功率對刻蝕速率影響較小���,如圖 (b)所示�。低溫刻蝕過程可以在較低的HF功率下進行���,因此�,等離體子對整個樣品的物理轟擊效果較弱,也使得掩?����?梢愿玫脑诳涛g過程中存在���,極大提高了刻蝕選擇比。

通常�����,光刻膠掩模選擇比大于100:1�����,二氧化硅掩模選擇比大于 200:1���,金屬的掩模選擇比則更高�����,大于2000:1�����。

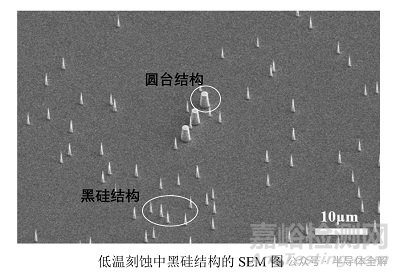

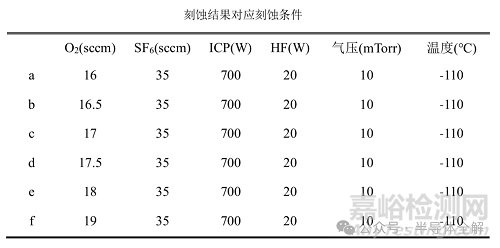

在刻蝕的過程中�����,降低HF功率或者增加氧氣氣體比例會導致表面生成的鈍化層無法完全去除�����,形成微掩模�,從而引發(fā)黑硅的形成,在無掩模位置出現(xiàn)雜草狀結構�����,如下圖所示�����。

為了避免這一現(xiàn)象�,ICP功率、HF功率以及氣體比例需要適配���。

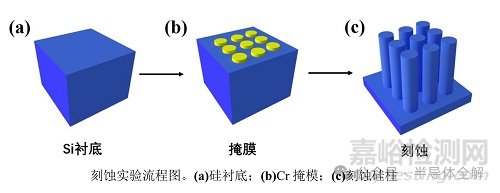

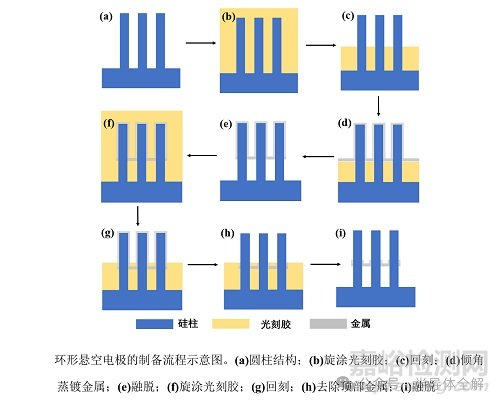

整個加工過程如下圖所示�。

首先�����,將襯底硅片清洗干凈,其步驟為丙酮�、酒精和水,分別超聲5分鐘�����。接著旋涂 PMMA正性光刻膠���,通過電子束曝光 (Electron Beam Lithography�,EBL)實現(xiàn)圖形化�。顯影定影后�,將樣品放入電子束蒸發(fā)(Electron Beam Deposition,EBD)設備中�,沉積40nm 金屬Cr薄膜,融脫后�����,形成Cr圓形掩摸�。緊接著將樣品送入ICP-RIE中進行低溫刻蝕實現(xiàn)Si柱結構。

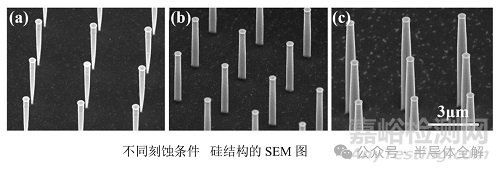

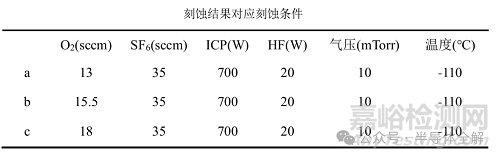

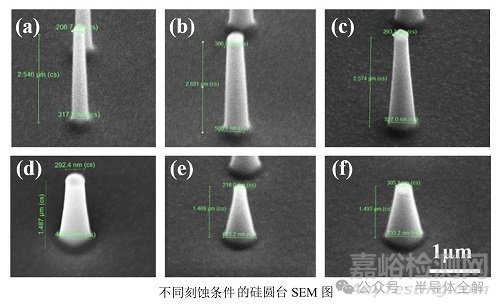

為了實現(xiàn)Si圓臺溝道形貌�,我們對刻蝕條件進行了研究,如下圖所示:

其對應刻蝕條件如下表所示。

圖(a)為上粗下細結構���,這種刻蝕結果主要是由于起鈍化作用的O2含量在氣體比例中偏低���,導致側壁形成的鈍化物無法有效阻止F-對橫向Si的刻蝕。

圖(b)顯示的刻蝕形貌基本上下直徑保持一致�,可以刻蝕出較為完美的圓柱、矩形等結構���。圖(c)則是上細下粗結構���,這種刻蝕形貌主要是起鈍化作用的O2含量在氣體比例中偏高,側壁形成的鈍化物較多���,垂直方向的物理轟擊不能及時去除���,一定程度上減弱了F-對 Si 的刻蝕效果,從而形成上細下粗的結構�����。

在刻蝕過程中���,主要通過改變氣體比例的方式實現(xiàn)對刻蝕柱狀的角度調控�。除此之外,調節(jié)氣壓�、ICP功率和HF功率也可以實現(xiàn)對刻蝕形貌的調控。例如���,適當增加HF功率可以加強垂直方向上的物理刻蝕效果�,從而更有效的去除水平方向上生成的副產(chǎn)物從而使得刻蝕結構更陡直�����。但HF功率也不宜過大�����,否則刻蝕選擇比會降低�����。適當增加反應腔室氣壓和ICP功率可以增大產(chǎn)生的等離子體密度從而增大刻蝕速率�,使得刻蝕形貌上細下粗情況 得到改善�����。

圖(a)~(f)顯示了通過改變氣體比例實現(xiàn)對上細下粗結構的形貌調控。

其刻蝕條件如下表所示�����。

需要指出的是不同掩模材料���、形狀和密度對刻蝕結果都有較為明顯的影響�����,在刻蝕過程中也需要考慮這些因素對刻蝕條件進行合理調節(jié)�。

除此之外�,載片的選擇對刻蝕結果也有較大影響,常用的載片有硅載片�、氧化硅/硅載片和石英載片,須在實驗中保持一致�����。為了達到穩(wěn)定可重復的刻蝕結果需要保持腔體環(huán)境穩(wěn)定�。在進行刻蝕實驗之前,需對設備腔體進行清洗�����,常用的清洗程序使用氣體為SF6和 O2。亦可開腔�����,對腔體進行清洗�。

三、Si溝道準博世(Pseudo Bosch)刻蝕工藝

低溫刻蝕工藝雖然可以實現(xiàn)高深寬比的Si圓柱�、圓臺結構,但在實際的半導體制造工藝中�����,由于需要大量液氮進行冷卻降溫�,提高了加工成本,同時由于在刻蝕硅圓臺結構時容易產(chǎn)生雜草狀結構不利于后續(xù)器件制備���,因此其并不是最佳的加工方案選擇�����。

常溫Pseudo Bosch工藝利用的氣體和Bosch工藝一致均為C4F8/SF6,但無需通過循環(huán)實現(xiàn)表面鈍化���,因此可以避免Bosch工藝的波紋效應���。

這也導致了其刻蝕深度無法和Bosch工藝相比���。在這一工藝中,SF6起到刻蝕作用�,C4F8 則是鈍化氣體,起到與低溫工藝中O2類似作用�。

SF6電離后提供F-、SFx等自由基來蝕刻硅�,蝕刻副產(chǎn)物為SiF4,可以被分子泵抽走�。C4F8電離后形成CF2聚合物鏈,沉積在樣品表面上�����。這種聚合物作為鈍化層可以保護Si 不被F-刻蝕�。

但是在垂直方向上由于存在HF源提供垂直偏置電場,因此水平表面的鈍化層會被物理刻蝕去除���,聚合物很難形成有效的水平表面鈍化層�����。而在側壁上生成的鈍化層則無法被有效去除���,可以保護樣品�,防止橫向刻蝕���。

這種方法相比較Bosch工藝�,減少了去除鈍化層工藝���,因此其刻蝕速率要比Bosch工藝慢�,但也避免了連續(xù)鈍化和去除鈍化層導致的波紋效應���,較慢的蝕刻速度和光滑的側壁使這種蝕刻方法成為納米級結構的理想工藝選擇�����。

Pseudo Bosch工藝和低溫刻蝕工藝最大的不同之處在于鈍化層的沉積速度不同�����,CF2聚合物的沉積速率相當快���,大約20-30nm/min。

為了進一步刻蝕硅材料�����,垂直方向的物理刻蝕過程應當保持一個較高速率以去除表面CF2 聚合物�����。因此���,控制垂直方向偏置電壓的HF源功率在Pseudo Bosch工藝中不可以太小�,以防止無法去除表面鈍化層�。

在上述兩種常用種刻蝕硅的加工工藝中,低溫刻蝕具有刻蝕速率快�����,掩模消耗小優(yōu)點�,但其需要液氮進行低溫冷卻,刻蝕后襯底不夠光滑�,在無掩模區(qū)域容易形成雜草狀結構。此外�,我們發(fā)現(xiàn)低溫刻蝕過程中的實驗氣體比例變化對刻蝕結果影響較大,刻蝕形貌對腔體環(huán)境也更為敏感���,不同狀態(tài)的腔體環(huán)境對刻蝕結果影響較為明顯�。相比之下,Pseudo Bosch工藝具備刻蝕形貌光滑�、工藝參數(shù)穩(wěn)定、可控性強�、無需大量液氮降溫成本低等優(yōu)勢,盡管其刻蝕速率和刻蝕選擇比相較于低溫刻蝕有所降低���,但某些條件下可以制備硅圓臺結構���。

四、三維環(huán)形懸空電極制備方法

上一節(jié)中���,我們利用Pseudo Bosch工藝加工了溝道半徑小于40nm�,高度1μm的硅圓臺結構�。接下來我們將討論如何制備三維結構上的環(huán)形懸空電極。這種方法不僅可以實現(xiàn)單個納米柱結構上的多個環(huán)形電極���,還可以實現(xiàn)多陣列大面積納米柱上的多層環(huán)形電極���。這種方法進一步提高了三維垂直晶體管的加工效率,實現(xiàn)多陣列�、高密度、大面積器件制備。

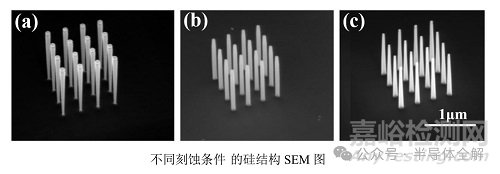

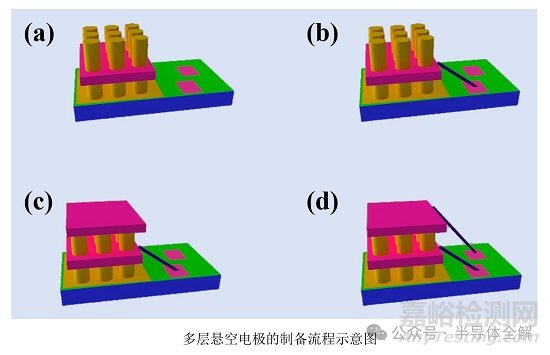

其制備流程示意圖如下圖所示�。

首先,在制備好的單根或陣列納米柱樣品上旋涂光刻膠���,旋涂厚度需大于硅柱高度,如圖 (b)�����。

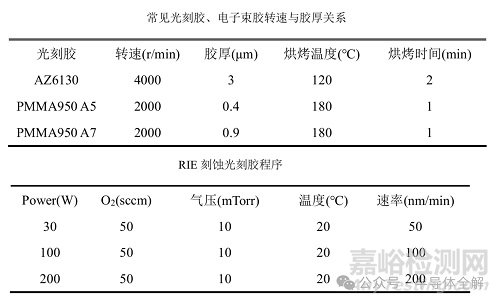

下表對應的是常用幾種光刻膠���、電子束膠的厚度與對應轉速關系�。

烘干樣品后�����,利用RIE進行回刻工藝�����,刻蝕參數(shù)如下表所示���,去除頂部多余光刻膠�����,如圖 (c)�����。

緊接著�,將樣品粘在10°傾角的樣品座上,然后放入具有自轉和公轉功能的熱蒸發(fā)設備�����,這種蒸鍍方法可以使金屬均勻包裹在硅柱表面���,如圖(d)�。蒸鍍完畢后�����,將樣品放入丙酮中浸泡���,溶脫后便可以的到如圖(e)所示的結構�����。

為了在硅柱中間形成環(huán)形懸空電極���,我們需要再次進行回刻工藝�����,旋涂光刻膠�,去除指定厚度光刻膠�����,利用濕法或者干法刻蝕工藝去除多余的金屬�,便形成如圖(e)所示的懸空電極�����。

通過控制RIE刻蝕時間可以精準的控制剩余金屬長度�����。

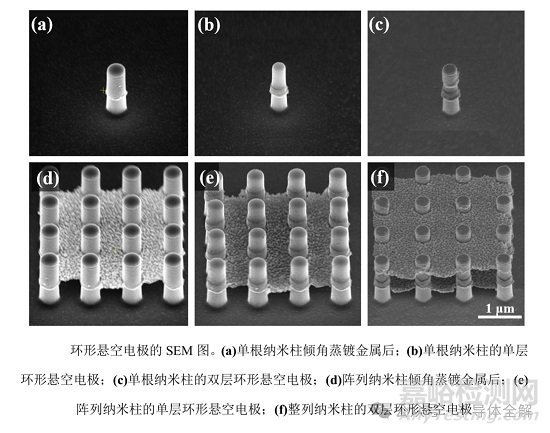

下圖是利用這一方法實際制備的懸空電極SEM圖���。

圖(a)(d)是單根�����、陣列納米柱第一次沉積金屬融脫后形成的結構�,從圖上可以看出利用傾角蒸鍍方法后金屬可以均勻的包裹在納米柱表面。

圖(b)(e)則是單根�����、陣列納米柱利用回刻法去除頂部多余金屬后形成的單層環(huán)形懸空電極�。圖(c)(f)則是利用同樣工藝實現(xiàn)的雙層環(huán)形懸空電極。這種環(huán)形懸空電極制備方法無需通過介質層實現(xiàn)電極隔離���,極大減少了電極之間的寄生效應�, 為后續(xù)三維垂直環(huán)柵器件電極的制備提供新的方案�。

四、基于FIB/FEB 技術的空間電極互聯(lián)方法

Pseudo Bosch 工藝刻蝕的硅圓臺垂直溝道結構和懸空電極制備完畢后�,電極互聯(lián)過程將通過FIB/FEB技術完成。

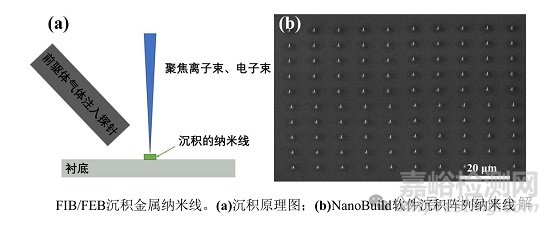

圖(a)是FIB/FEB沉積金屬納米線示意圖���。

具體的實驗方法是:首先設置離子束���、電子束工作模式為點掃描模式,插入前驅體氣體注入探針后�����,打開前驅體使樣品附近處的氣體濃度平衡,接著打開離子束或者電子束�,經(jīng)過指定時間后便可以獲得指定高度的金屬納米線。待腔體真空恢復到沉積之前���,打開電子束進行觀察�。沉積所得金屬納米線的直徑�、表面光滑程度和高度一方面受離子束、電子束工作狀態(tài)決定�,如加速電壓、束流���、聚焦相散等。另一方面由前驅體源氣體分子決定�,如樣品距前驅體源距離,前驅體源氣流速度等�����。

通過FIB/FEB 技術不僅可以實現(xiàn)上述單層懸空電極到平面電極的互聯(lián)�����,還可以實現(xiàn)多層懸空電極的互聯(lián)。

我們通過“自下而上”的辦法實現(xiàn)多層懸空電極的制備及其與平面電極的互聯(lián)�,其實驗過程如示意圖所示。

首先�,如圖(a)所示制備高度較低的第一層懸空電極,并且通過上述方法實現(xiàn)平面到空間電極互聯(lián), 如圖(b)�����。接著再次利用上述方法制備高度較高的第二層懸空電極���,如圖(c)���,然后利用FIB/FEB實現(xiàn)第二層懸空電極與平面電電極的連接,如圖(d)���。

通過這種方法可以在高深寬比的三維垂直結構上制備多層懸空電極以滿足多功能納米器件的應用需求�����。

五���、硅基三維垂直環(huán)柵無結場效應晶體管加工流程

以下工藝流程以設計加工半徑 40 nm、高度1μm的硅圓臺作為溝道�,以實現(xiàn)柵極控制能力更強的三維垂直環(huán)柵無結場效應晶體管制備���。

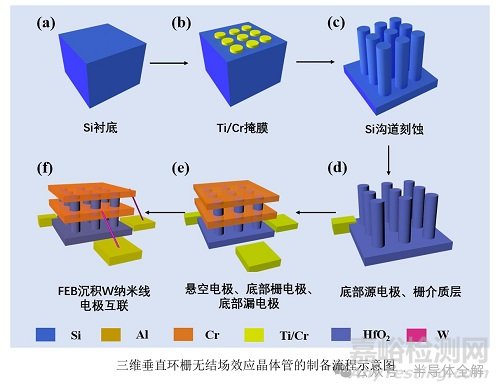

整個器件的制備流程圖如下圖所示。

第一步:制備垂直硅納米柱溝道�����。

選擇n型摻雜濃度為1×10E18 cm-3的(100)硅片�����,分別使用丙酮���、異丙醇�、去離子水進行超聲清洗���,超聲時間五分鐘。110 ℃烘干后�����,旋涂PMMA 495 A5正性電子束光刻膠���。

通過電子束曝光定義圖形���,顯影定影后�,在樣品表面沉積Ti/Cr(40nm/40nm)雙層金屬�����。

融脫后形成圓形金屬掩模�,如圖(b)。

利用ICP-RIE中Pseudo Bosch工藝實現(xiàn)硅納米圓臺刻蝕�。

利用濕法腐蝕的辦法去除Cr掩模,如圖(c)�����。

第二步:定義平面源電極和柵介質層�����。

在樣品表面旋涂800nm的電子束光刻膠���,EBL定義平面源電極�����,EBD生長20nm的Ti 形成平面源電極�。溶脫后,將樣品送入快速退火爐在氮氣氛圍下���,850 ℃下退火五分鐘�,形成平面源電極和頂部漏電極歐姆接觸�����。接著將樣品放入原子層沉積中生長10nm氧化鉿�。

第三步:定義平面柵電極和漏電極。

再次旋涂800nm正性光刻膠���,通過EBL以及EBD制備200nm金屬Al實現(xiàn)平面源�����、柵電極�����。

第四步:制備環(huán)形懸空柵電極,并利用FEB沉積的金屬W納米線實現(xiàn)環(huán)形懸空柵電極與平面柵電極的互聯(lián)�����。

第五步:制備懸空頂部漏電極,并利用FEB沉積的金屬W納米線實現(xiàn)頂部懸空漏電極與平面漏電極的互聯(lián)�。

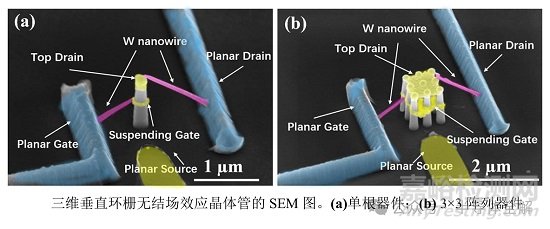

制備好的單根與陣列三維垂直環(huán)柵器件如下圖所示。