所謂的“TSV”,就是“Through Silicon Via”的英文縮寫(xiě)�。從字面意思上翻譯來(lái)看���,是“直通硅穿孔”,至于它的定義和作用���,則要從半導(dǎo)體的封裝技術(shù)說(shuō)起���。

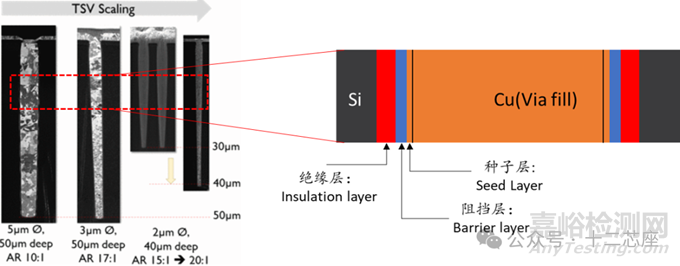

TSV(Through Silicon Via),硅通孔技術(shù)���,是通過(guò)硅通道垂直穿過(guò)組成堆棧的不同芯片或不同層實(shí)現(xiàn)不同功能芯片集成的先進(jìn)封裝技術(shù)���。TSV 主要通過(guò)銅等導(dǎo)電物質(zhì)的填充完成硅通孔的垂直電氣互連,減小信號(hào)延遲���,降低電容���、電感,實(shí)現(xiàn)芯片的低功耗���、高速通信�����,增加帶寬和實(shí)現(xiàn)器件集成的小型化需求���。

就像我們一般在收納物品放置的道理一樣,從平鋪到堆疊�����,故物品越多后就會(huì)成為三維排列的體積來(lái)增加空間利用率�����。

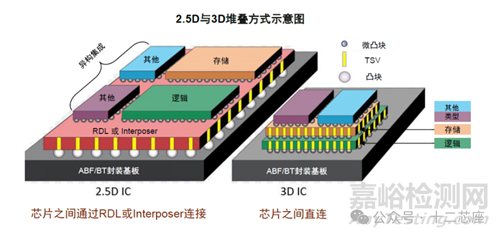

而半導(dǎo)體芯片堆疊�����,也是相同的概念�����。當(dāng)芯片的功能越來(lái)越強(qiáng)大�、越來(lái)越復(fù)雜后,其單一個(gè)計(jì)算單元已無(wú)法滿(mǎn)足的要求���,這時(shí)候?qū)?huì)增加各種不同的單元以擴(kuò)張芯片的計(jì)算能力�����。這時(shí)候除了主運(yùn)算功能的芯片外���,還可依據(jù)實(shí)際需求會(huì)有很多周邊功能的芯片���,并以二維的方式分散在其周?chē)?當(dāng)越多芯片單元需要存在的情況下,則可以考慮在最佳效率的前提下�,故而產(chǎn)生往三維堆疊所為的“3D IC”一詞;

此前�,芯片之間的大多數(shù)連接都是水平的,TSV 的誕生讓垂直堆疊多個(gè)芯片成為可能�����。Wire bonding(引線(xiàn)鍵合)和 Flip-Chip(倒裝焊)的 Bumping(凸點(diǎn))提供了芯片對(duì)外部的電互連���,RDL(再布線(xiàn))提供了芯片內(nèi)部水平方向的電互連���,TSV 則提供了硅片內(nèi)部垂直方向的電互連。

TSV 三種主要應(yīng)用方向:背面連接�、2.5D 封裝、3D 封裝TSV 有多種用途,可大致分為 3 種:

垂直的背面連接���,無(wú)芯片堆疊�����,如“簡(jiǎn)單的背面連接”。TSV 位于有源晶粒(active die)中�,用于連接至晶圓背面的焊盤(pán)(bond pad);

2.5D 封裝�。晶粒(die)連接至硅中介層(interposer),TSV 在中介層中�����;

3D 封裝�。TSV 位于有源晶粒中,用于實(shí)現(xiàn)芯片堆疊�。

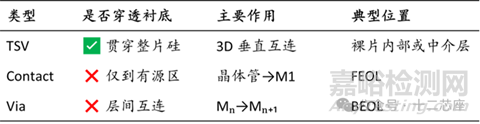

TSV 與其他“孔”的區(qū)別

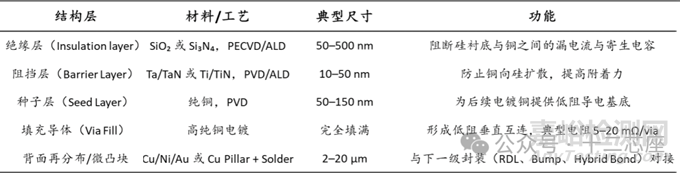

TSV 的完整結(jié)構(gòu)

Summary

目前,TSV技術(shù)在行業(yè)中已經(jīng)屬于關(guān)鍵工藝�,對(duì)于制造高端芯片非常重要,廣泛應(yīng)用于存儲(chǔ)器(例如堆疊式DRAM)�、處理器、圖像傳感器等高性能芯片中�。

Reference:

1.https://www.otsuka-tw.com/technical_articles-detail/TSV/

2.Wafer-On-Wafer-On-Wafer (WoWoW) Integration Having Large-scale High Reliability Fine 1 μm Pitch Face-To-Back (F2B) Cu-Cu Connections and Fine 6 μm Pitch TSVs.

3.Nano-Through Silicon Vias (nTSV) for Backside Power Delivery Networks (BSPDN)