一���、芯片堆疊技術:從平面到立體的產(chǎn)業(yè)革命

2025年11月�����,沙特阿卜杜拉國王科技大學的科學家們創(chuàng)造了半導體行業(yè)的新紀錄——成功研制出擁有6層功能電路的混合CMOS芯片����,將此前不超過兩層的堆疊極限提升了三倍����。這項被稱為"微芯片摩天樓"的創(chuàng)新,標志著半導體產(chǎn)業(yè)正式進入"垂直革命"時代。當傳統(tǒng)平面工藝的晶體管密度已接近每平方毫米1億個的物理上限�����,芯片制造商們正像城市建設者轉向高空發(fā)展一樣��,開始了"向上生長"的轉型���。

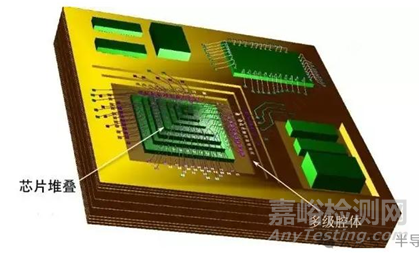

芯片堆疊技術,準確來說應稱為三維堆疊封裝技術(3D Stacking Packaging)�,是通過垂直互聯(lián)將多個芯片或功能層在Z軸方向堆疊集成�����,實現(xiàn)高密度互連的先進技術���。其核心在于通過硅通孔(TSV,硅通孔技術�,相當于芯片內(nèi)部的立體高速公路)����、微凸點(Microbump) 和混合鍵合(Hybrid Bonding) 等關鍵工藝,突破傳統(tǒng)平面封裝的物理限制。根據(jù)堆疊方式的不同����,可分為芯片級堆疊(如HBM)����、晶圓級堆疊(如WoW)和封裝級堆疊(如PoP)三大類。

1)為什么需要堆疊上百層?

想象一下��,如果把傳統(tǒng)平面芯片比作單層平房���,三維堆疊芯片就是摩天大樓���。當城市土地資源(芯片面積)有限時�,向高空發(fā)展是必然選擇�。從技術演進看,堆疊層數(shù)的增加源于三個維度的迫切需求:

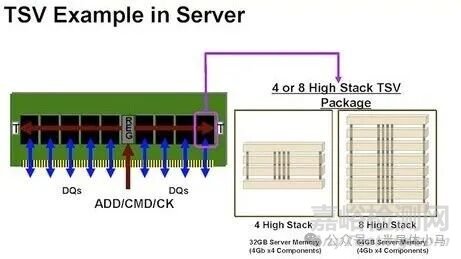

性能需求維度:AI大模型訓練需要每秒數(shù)十TB級的數(shù)據(jù)帶寬���,傳統(tǒng)平面布局的內(nèi)存與計算單元之間如同隔著繁忙的城市主干道,數(shù)據(jù)傳輸延遲嚴重制約性能���。通過3D堆疊實現(xiàn)的高帶寬存儲器(HBM) 技術�����,帶寬可達TB/s級別,較傳統(tǒng)GDDR6提升3倍以上����,功耗降低30%。NVIDIA H100 GPU通過堆疊8層DRAM芯片����,實現(xiàn)了3.3TB/s的內(nèi)存帶寬�,這相當于每秒鐘傳輸165部4K電影的數(shù)據(jù)量�����。

物理極限維度:當晶體管柵極長度逼近1nm時�����,量子隧穿效應導致漏電率飆升��,傳統(tǒng)平面工藝已觸及物理天花板�����。垂直堆疊技術能將晶體管密度提升數(shù)倍�,沙特研究團隊開發(fā)的6層堆疊結構在相同"占地面積"下實現(xiàn)了晶體管數(shù)量的指數(shù)級增長,這種密度提升帶來的性能飛躍是平面工藝無法企及的����。

成本優(yōu)化維度:平面工藝每提升一代,晶圓廠建設成本就要增加30%以上�,3nm產(chǎn)線投資高達200億美元。而垂直堆疊技術通過復用底層工藝��、減少芯片面積�����,能將單位功能成本降低40%���。據(jù)Yole Développement預測,2027年3D堆疊市場規(guī)模將超120億美元��,年復合增長率達19%,證明了其商業(yè)價值��。

2)從AI芯片到可穿戴設備:堆疊技術的多元應用場景

高性能計算領域已成為3D堆疊技術的主戰(zhàn)場��。AMD的3D V-Cache技術通過在Zen4 CPU核心上方堆疊64MB SRAM緩存,使游戲性能提升15%~25%���,緩存延遲從傳統(tǒng)2D設計的約70ns降至約10ns����,降幅達85%�����。蘋果M系列芯片采用3D堆疊技術實現(xiàn)CPU���、GPU和內(nèi)存的異構集成�����,在Mac Studio中���,M1 Ultra通過UltraFusion技術將兩個M1 Max芯片連接���,帶寬達2.5TB/s,相當于在兩個芯片間構建了16條40車道的超級高速公路����。

移動設備領域同樣受益顯著����。三星Galaxy S23系列采用的Exynos 2300處理器通過PoP(Package on Package)堆疊技術,將AP和DRAM集成在同一封裝內(nèi)��,使PCB面積減少30%����,為電池騰出更多空間����。華為Mate 60 Pro的麒麟9000S芯片采用自研的3D堆疊方案,在有限體積內(nèi)實現(xiàn)了5G基帶與應用處理器的高效集成���。

存儲領域是3D堆疊技術最成熟的應用場景�。三星238層3D NAND單芯片容量達2TB����,SSD產(chǎn)品順序讀取速度突破7,450MB/s;SK海力士的HBM3內(nèi)存通過8層堆疊實現(xiàn)了64GB容量����,成為AI服務器的"標配"。據(jù)CFM閃存市場數(shù)據(jù)��,2024年服務器NAND容量暴增108%�����,HBM更是增長了311%,這些都離不開堆疊技術的支撐�����。

二�、三大技術難關與行業(yè)突破方案

1)散熱管理:給芯片裝上"中央空調(diào)"

當多個發(fā)熱芯片堆疊在一起,就像把幾臺暖氣爐塞進一個密閉空間���,散熱挑戰(zhàn)呈指數(shù)級增長����。3D堆疊結構的熱流密度可達500 W/cm²����,相當于火箭發(fā)動機噴嘴處的熱強度。傳統(tǒng)風冷方案在處理1000瓦設備時�����,風扇功耗高達20%�,而I²R損耗也占據(jù)10%到20%��。

微流體冷卻技術成為高端芯片的"救命稻草"。臺積電推出的硅集成微冷卻器(IMEC-Si)架構����,在10升/分鐘水流條件下可耗散超過3,000瓦的均勻功率��,熱阻低至0.15℃/W����。SK海力士在HBM存儲器中引入微通道液冷系統(tǒng),實測可使芯片溫度降低28℃���。AMD高級副總裁Sam Naffziger透露��,采用直接液體冷卻的服務器��,總功耗可降低40%�����,因為不再需要為散熱風扇分配大量電力����。

新型散熱材料也發(fā)揮關鍵作用����。3M公司研發(fā)的新型導熱凝膠材料熱導率達25W/m·K�����,是傳統(tǒng)硅材料的8倍���;石墨烯散熱膜則憑借其超高導熱性能(5000W/m·K),成為移動設備堆疊芯片的理想選擇����。華為P60 Pro采用石墨烯-蒸汽室復合散熱系統(tǒng),成功將堆疊芯片的熱量均勻導出�。

2)互聯(lián)密度:突破納米級的"高空索道"

芯片間的互聯(lián)就像摩天大樓之間的空中走廊,既要足夠密集以滿足數(shù)據(jù)傳輸需求�,又要保證連接的可靠性���。傳統(tǒng)引線鍵合技術如同單車道小橋�,已無法滿足AI時代的"交通流量"�����。

硅通孔(TSV)技術是垂直互聯(lián)的"高速公路"���。這項技術通過在硅片中垂直鉆通孔,實現(xiàn)層間高速信號傳輸���,直徑約5~10μm的TSV如同納米級的"深井"�����,需要精確的深寬比控制和電鍍填充工藝��。SK海力士HBM3內(nèi)存通過TSV實現(xiàn)邏輯芯片與存儲器的垂直集成���,帶寬較GDDR6提升3倍以上��。

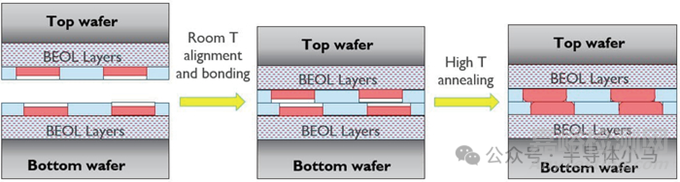

混合鍵合技術則代表了互聯(lián)技術的未來方向���。不同于傳統(tǒng)的焊料凸點連接,混合鍵合直接實現(xiàn)銅-銅界面的原子級鍵合�,間距可縮小至1μm以下。臺積電SoIC技術的混合鍵合間距已達1μm���,互連密度較傳統(tǒng)微凸塊提升15倍��,速度提升11.9倍���,帶寬密度實現(xiàn)191倍之高。據(jù)Besi預測�,到2030年混合鍵合設備市場規(guī)模將達3.97億美元。

3)良率控制:三維時代的"積木游戲"

多層堆疊如同搭建復雜的積木塔�����,每增加一層�,失敗的風險就會累積。傳統(tǒng)2D芯片良率只需考慮單個平面�,而3D堆疊的復合良率是各層良率的乘積——如果每層良率是90%����,10層堆疊后的總體良率僅為34.8%����。

已知良好芯片(KGD)篩選是提升良率的關鍵。英特爾Foveros技術通過在堆疊前對每顆芯片進行嚴格測試����,只將合格芯片用于堆疊,使10層堆疊的良率提升至70%以上����。臺積電CoWoS工藝良率已突破60%����,較2022年提升了25個百分點��,這背后是原子層沉積(ALD)和電化學鍍銅等先進工藝的支撐���。

冗余設計技術也不可或缺��。三星在其12層堆疊的HBM4中引入了TSV冗余修復機制��,當檢測到某個TSV失效時����,系統(tǒng)會自動切換至備用通道�,就像高速公路的應急車道,保障數(shù)據(jù)傳輸不中斷���。這種設計使HBM4的有效良率提升了15%����。

三、商業(yè)價值與產(chǎn)業(yè)變革

性能與成本的平衡藝術

3D堆疊技術雖然初期投資巨大��,但帶來的性能提升足以抵消成本增加�。AMD銳龍9 7950X處理器通過3D V-Cache技術�����,L3緩存容量從32MB提升至128MB,游戲性能提升15%~25%��,而額外成本僅增加10%����。據(jù)日經(jīng)新聞產(chǎn)業(yè)調(diào)查�����,采用3D堆疊的AI芯片雖然封裝成本增加35%���,但由于性能提升帶來的服務器數(shù)量減少,數(shù)據(jù)中心總體擁有成本(TCO)反而降低20%���。

成本結構正在發(fā)生變化�����。傳統(tǒng)2D封裝中,封裝成本占芯片總成本的10%~15%����,而先進3D封裝可達到30%~40%。但臺積電業(yè)務發(fā)展高級副總裁張曉強指出:"晶體管技術和先進封裝集成必須攜手共進����,才能為客戶提供完整的產(chǎn)品級解決方案�����。三維架構技術組合對我們來說已經(jīng)變得非常重要�����。"這種投入是必要的�,因為單純依靠制程微縮的時代已經(jīng)結束�。

產(chǎn)業(yè)格局的重構力量

3D堆疊技術正在打破半導體產(chǎn)業(yè)的傳統(tǒng)格局��。過去��,制程節(jié)點是衡量競爭力的唯一標準�����,而現(xiàn)在封裝技術成為新的競爭焦點����。臺積電憑借CoWoS和SoIC技術組合���,占據(jù)全球高端封裝市場60%以上份額����;英特爾雖然在先進制程落后��,但憑借EMIB和Foveros封裝技術�����,成為蘋果和高通評估的潛在替代方案;三星則通過X-Cube技術����,在HBM市場占據(jù)領先地位�。

供應鏈重構正在發(fā)生。封測廠不再只是產(chǎn)業(yè)鏈的"后端"環(huán)節(jié)��,而成為技術創(chuàng)新的核心參與者����。長電科技XDFOI平臺實現(xiàn)20μm芯片間距突破�����,通富微電VISionS技術攻克2.5D中介層量產(chǎn)難題�,這些進展使中國封測企業(yè)在全球市場的份額提升至38%����。正如華天科技CEO肖勝利所言:"先進封裝讓封測廠從'體力勞動者'轉變?yōu)?#39;技術創(chuàng)新者'。"

四����、專家洞見與未來展望

臺積電CEO魏哲家在2025年技術論壇上強調(diào):"3D集成不是簡單的技術選擇��,而是生存必需����。當2nm制程面臨物理極限時�,垂直方向的創(chuàng)新將決定未來十年的產(chǎn)業(yè)格局。"公司計劃2026年底前將CoWoS產(chǎn)能從100kwpm擴大至120-130kwpm�,以滿足AI芯片的爆發(fā)需求��。

英特爾代工高級副總裁兼總經(jīng)理Kevin O'Buckley則指出:"每個人都在談論內(nèi)存墻問題����。隨著我們不斷增加內(nèi)核數(shù)量�����,并將計算性能推向更高水平,首要任務就是滿足數(shù)據(jù)處理的需求��。3D就是一個例子,我們可以利用芯片面積的很大一部分來放置SRAM�����,而無需犧牲那些仍然需要用于計算的芯片面積��。"

IMEC(比利時微電子研究中心)總裁Luc Van den hove提出的"CMOS 2.0"愿景�����,將3D堆疊提升到新高度:"下一個時代將不僅僅由更小的晶體管定義����,它將涉及三維功能集成,以克服二維縮放的瓶頸����。"該構想通過背面供電���、細間距混合鍵合�����、CFET晶體管和雙面工藝四大支柱�,重新定義半導體制造。

技術演進路線圖

短期(2025-2027):混合鍵合間距將從目前的1μm縮小至0.5μm�,HBM堆疊層數(shù)從12層增至16層��,3D NAND閃存將突破400層。臺積電SoIC技術將實現(xiàn)邏輯芯片與存儲的直接鍵合����,帶寬較傳統(tǒng)中介層提升5倍�。

中期(2028-2030):互補場效應晶體管(CFET) 將實現(xiàn)量產(chǎn),垂直堆疊n型和p型晶體管�,標準單元密度較GAA提升30%~40%�����。微流體冷卻將成為高端芯片的標配����,散熱效率較傳統(tǒng)風冷提升3倍。

長期(2030年后):光電混合堆疊技術將突破電互連的物理限制����,硅光子層與電子層的集成實現(xiàn)Tb/s級片間通信。三維異質(zhì)集成將成為主流�����,不同材料(硅��、GaN����、SiC)和不同功能(邏輯�、存儲、傳感器)的芯片將無縫集成在單一封裝中�。

五�����、讀者問答:解開3D堆疊的疑惑

Q1: 3D堆疊芯片會更耗電嗎?

A: 不會��。雖然堆疊增加了芯片密度����,但通過縮短互連線長度����,3D堆疊反而能降低功耗�����。AMD 3D V-Cache技術使緩存訪問功耗降低50%�,NVIDIA H100的HBM3內(nèi)存功耗較GDDR6降低30%���。關鍵在于采用先進的散熱設計,避免熱量積聚影響能效�。

Q2: 手機什么時候能用上10層堆疊芯片?

A: 部分旗艦手機已經(jīng)實現(xiàn)。三星Galaxy S23 Ultra采用的Exynos 2300處理器使用4層堆疊設計�,將CPU�、GPU和ISP集成在一起。隨著混合鍵合成本下降���,2026年中端手機有望采用6層堆疊芯片��,實現(xiàn)更強的AI算力和更長續(xù)航�����。

Q3: 3D堆疊會讓摩爾定律失效嗎?

A: 恰恰相反����,3D堆疊是延續(xù)摩爾定律的關鍵。當平面制程逼近物理極限��,垂直方向的擴展成為新的增長維度�����。IMEC預測,通過3D集成��,到2030年系統(tǒng)級晶體管密度仍能保持每三年翻一番的速度增長�,延續(xù)摩爾定律的精髓����。

Q4: 中國在3D堆疊領域處于什么水平?

A: 部分技術已達國際先進水平�。長電科技�����、通富微電等企業(yè)在中高端封裝領域已實現(xiàn)突破����。但在高端設備和材料方面�����,仍依賴進口����,需持續(xù)攻關��。

Q5: 3D堆疊芯片維修會更困難嗎��?

A: 是的����,但通過模塊化設計可緩解��。如同現(xiàn)代建筑采用預制構件��,3D堆疊芯片可設計為可替換的芯片組����,某一層出現(xiàn)故障時無需更換整個芯片����。英特爾Foveros技術支持芯片層的單獨更換,降低維修成本�����。未來隨著技術成熟�,維修難度將進一步降低�����。