一��、問題概述

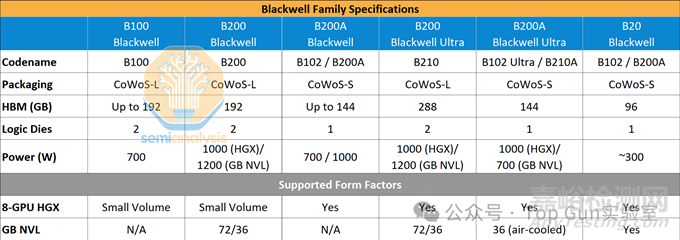

英偉達(dá)(Nvidia)Blackwell架構(gòu)芯片在24年下半年的生產(chǎn)延遲�����,主要源于其首次大規(guī)模采用的臺(tái)積電(TSMC)CoWoS-L封裝技術(shù)在初期量產(chǎn)階段的良率極低��。根據(jù)SemiAnalysis的深度分析�����,該問題的根源在于Blackwell復(fù)雜的雙芯片(Dual-die)設(shè)計(jì)與CoWoS-L封裝工藝在熱機(jī)械穩(wěn)定性上的不匹配��,導(dǎo)致了嚴(yán)重的物理失效�����。

二、技術(shù)背景:CoWoS-L 的架構(gòu)演進(jìn)

為了實(shí)現(xiàn) Blackwell 巨大的算力需求���,英偉達(dá)從傳統(tǒng)的CoWoS-S轉(zhuǎn)向了更具擴(kuò)展性的CoWoS-L封裝��。

2.1 CoWoS-L結(jié)構(gòu)解析

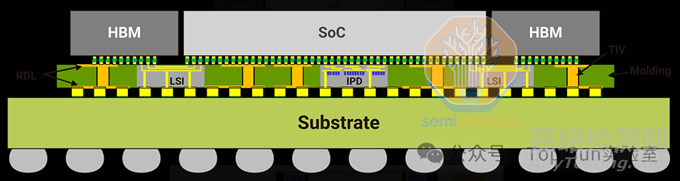

CoWoS-L使用RDL(再分布層)中介層���,并在其中嵌入LSI(局部硅互連)橋接芯片��。這種設(shè)計(jì)允許在有機(jī)基板上拼接多個(gè)大型芯片��,突破了傳統(tǒng)硅中介層的尺寸限制�����。

2.2 與CoWoS-S的對(duì)比

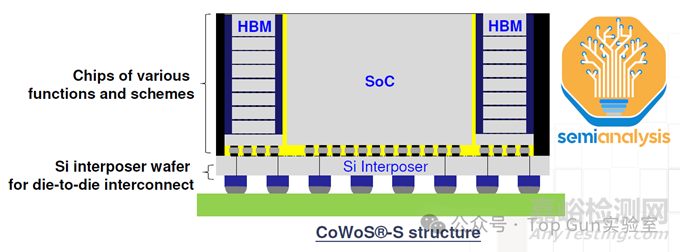

傳統(tǒng)的CoWoS-S使用一整塊硅中介層(Silicon Interposer)��,雖然工藝成熟���,但受限于光罩尺寸(Reticle Size)���,且大面積硅片極其脆弱。

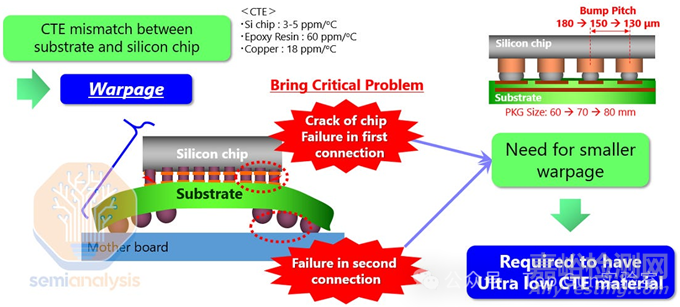

Blackwell在封裝過程中遇到的核心挑戰(zhàn)是熱膨脹系數(shù)(CTE)不匹配導(dǎo)致的物理損壞�����。

3.1 CTE不匹配與翹曲(Warpage)

o失效機(jī)制:CoWoS-L封裝包含硅芯片(GPU/LSI)�����、有機(jī)RDL中介層和PCB基板��。這些材料的CTE差異巨大(硅≈3ppm/°C�����,有機(jī)材料則高得多)��。

o后果:在生產(chǎn)過程的高溫環(huán)境下�����,不同材料膨脹比例不一�����,導(dǎo)致封裝體產(chǎn)生嚴(yán)重的翹曲��。繼而引發(fā)微凸點(diǎn)(Micro-bumps)斷裂,導(dǎo)致芯片間通信失效�����。

3.2 LSI橋接芯片的對(duì)準(zhǔn)與設(shè)計(jì)缺陷

o精度挑戰(zhàn):Blackwell的雙芯片互連帶寬高達(dá)10TB/s�����,對(duì)LSI橋接芯片的放置精度要求極高��。

o設(shè)計(jì)重制:由于初期良率極低���,英偉達(dá)不得不重新設(shè)計(jì)LSI橋接芯片,并修改了GPU芯片頂層的金屬層和凸點(diǎn)布局��,以增強(qiáng)結(jié)構(gòu)強(qiáng)度并緩解應(yīng)力��。

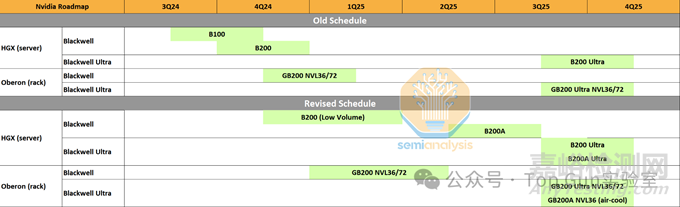

四��、生產(chǎn)影響與路線圖調(diào)整

由于CoWoS-L的良率問題��,英偉達(dá)被迫推遲了大規(guī)模出貨時(shí)間��,并調(diào)整了產(chǎn)品線�����。

4.1 B200A的戰(zhàn)略角色

為了繞過CoWoS-L的產(chǎn)能和良率瓶頸,英偉達(dá)緊急推出了B200A��。

o單芯片設(shè)計(jì):B200A采用單顆B102芯片�����,無需復(fù)雜的雙芯片互連�����。

o回歸成熟工藝:B200A可以使用更成熟的CoWoS-S封裝�����,從而保障了中低端市場的供應(yīng)���。

5. 結(jié)論

英偉達(dá)修改了GPU芯片頂層的金屬層和凸點(diǎn)布局�����,增強(qiáng)了結(jié)構(gòu)強(qiáng)度��。這一修復(fù)在24年底完成�����,為25年的大規(guī)模量產(chǎn)掃清了障礙�����。截至當(dāng)前���,Blackwell芯片已實(shí)現(xiàn)全球范圍內(nèi)的超大規(guī)模交付�����,初期的封裝危機(jī)已完全成為過去式��。

Blackwell的封裝危機(jī)反映了AI芯片向超大規(guī)模異構(gòu)集成演進(jìn)中的技術(shù)風(fēng)險(xiǎn)��。Blackwell的“封裝危機(jī)”雖然在24年造成了約一個(gè)季度的延遲���,但英偉達(dá)與臺(tái)積電的快速修復(fù)以及臺(tái)積電專門用于CoWoS-L的AP6工廠產(chǎn)能釋放確保了25年的爆發(fā)式增長��。目前�����,Blackwell不僅實(shí)現(xiàn)了大規(guī)模交付,其迭代版本Blackwell Ultra也已確立了市場統(tǒng)治地位���。