2025年�����,全球半導(dǎo)體產(chǎn)業(yè)在挑戰(zhàn)與機(jī)遇中穩(wěn)步前行�。據(jù)世界半導(dǎo)體貿(mào)易統(tǒng)計(jì)協(xié)會(WSTS)數(shù)據(jù)顯示����,2025年全球半導(dǎo)體市場規(guī)模預(yù)計(jì)超過7,000億美元,同比增長約11.2%�,其中人工智能(AI)與高性能計(jì)算(HPC)相關(guān)芯片增速顯著���,推動了先進(jìn)工藝、封裝及存儲技術(shù)的不斷創(chuàng)新�����。

在技術(shù)層面�,2nm工藝節(jié)點(diǎn)進(jìn)入量產(chǎn)關(guān)鍵階段,臺積電N2工藝晶體管密度成為行業(yè)標(biāo)桿�����;英特爾18A工藝憑借環(huán)柵場效應(yīng)管(GAAFET)與背面供電網(wǎng)絡(luò)(BSPDN)技術(shù)的創(chuàng)新應(yīng)用�����,實(shí)現(xiàn)性能與能效的雙重突破���。

與此同時(shí)�����,存算一體�����、芯粒(Chiplet)�����、共封裝光學(xué)(CPO)等前沿技術(shù)加速落地��。北京大學(xué)�����、南京大學(xué)�、中科院微電子所等機(jī)構(gòu)在存算一體領(lǐng)域取得突破性進(jìn)展;imec成功實(shí)現(xiàn)250nm間距的3D鍵合�,為邏輯-內(nèi)存異構(gòu)集成提供關(guān)鍵支撐;英偉達(dá)推出集成硅光引擎的CPO交換芯片����,顯著提升能效與部署效率,推動該技術(shù)在AI超級集群中走向早期應(yīng)用�。

面對摩爾定律逐漸接近物理極限,半導(dǎo)體產(chǎn)業(yè)正從“單點(diǎn)突破”轉(zhuǎn)向“系統(tǒng)級創(chuàng)新”����。2025年��,一部分新型半導(dǎo)體技術(shù)已從驗(yàn)證階段邁入規(guī)模化應(yīng)用的臨界點(diǎn)����,為2026年的全面落地奠定堅(jiān)實(shí)基礎(chǔ)。在AI驅(qū)動�����、算力需求爆發(fā)的背景下��,這些技術(shù)突破將重塑芯片設(shè)計(jì)�����、制造與應(yīng)用的全鏈條�����,引領(lǐng)半導(dǎo)體產(chǎn)業(yè)進(jìn)入新一輪增長周期���。

《電子工程專輯》基于這一年中與業(yè)內(nèi)專家和廠商的交流����,總結(jié)分析后挑選出了2026年全球半導(dǎo)體將出現(xiàn)或高速發(fā)展的10大技術(shù)趨勢,本文將探討這些先進(jìn)技術(shù)的發(fā)展方向和市場前景��。

趨勢一:BSPDN引領(lǐng)先進(jìn)工藝革新

作者:劉于葦

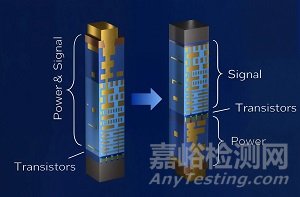

BSPDN正成為突破先進(jìn)工藝物理瓶頸的核心技術(shù)之一���,預(yù)計(jì)在2026年全面進(jìn)入量產(chǎn)爬坡與生態(tài)擴(kuò)展的關(guān)鍵階段�����。該技術(shù)通過將傳統(tǒng)位于晶圓正面的供電線路遷移至背面���,利用納米級硅穿孔(nTSV)或埋藏式電源軌(BPR)實(shí)現(xiàn)電力垂直傳輸,從而在物理空間上解耦電源與信號布線�。此舉不僅大幅縮短供電路徑、降低IR壓降(電壓損耗)����,更釋放了正面金屬層資源,用于高密度信號互聯(lián)���,顯著提升信號完整性與晶體管集成密度�,為2nm及以下節(jié)點(diǎn)提供可持續(xù)的功耗�����、性能和面積(PPA)優(yōu)化路徑。

當(dāng)前���,Intel、臺積電與三星三大代工巨頭均已在BSPDN領(lǐng)域展開布局�����。Intel憑借其PowerVia技術(shù)�����,結(jié)合RibbonFET GAAFET�����,計(jì)劃在其18A工藝節(jié)點(diǎn)中引入BSPDN,并已進(jìn)入量產(chǎn)爬坡階段����。根據(jù)在2025年VLSI研討會上的系統(tǒng)比較,Intel 18A工藝通過采用GAAFET和BSPDN技術(shù)�����,在相同電壓(1.1V)下�����,相比Intel 3工藝頻率可提升25%�,或功耗降低36%;在0.75V低壓下����,性能提升18%,功耗減少38%�。此外,BSPDN的引入使得正面M0層間距得以放寬�����,降低了制造復(fù)雜度與良率風(fēng)險(xiǎn)���。

正面與背面供電���。(來源:Intel)

臺積電計(jì)劃在2026年下半年推出的A16節(jié)點(diǎn)中集成GAAFET與背面接觸供電技術(shù)�����,宣稱通過優(yōu)化布線資源使用效率,可實(shí)現(xiàn)7-10%的芯片密度提升與20%的能效提升��。三星則宣布將在2027年SF2Z節(jié)點(diǎn)引入背面供電�����,采用直接背面接觸設(shè)計(jì)����,目標(biāo)性能提升8%���,功耗降低15%���,芯片面積減少7%。

技術(shù)層面���,BSPDN將與GAAFET�、3D互連深度融合,通過縮小標(biāo)準(zhǔn)單元高度(如Intel 18A高性能單元壓縮至180nm)��、優(yōu)化金屬層堆疊(22層結(jié)構(gòu)+背面金屬隔離)�,提升晶體管密度,滿足HPC�、AI算力需求。同時(shí)�,CMOS 2.0架構(gòu)推動SoC垂直堆疊���,imec已實(shí)現(xiàn)250nm間距3D鍵合��,支持邏輯-內(nèi)存異構(gòu)集成。產(chǎn)業(yè)生態(tài)上���,廠商通過光刻校正將鍵合誤差控制在25nm內(nèi),但全晶圓良率提升仍需工具突破���。

預(yù)計(jì)2026年BSPDN將加速量產(chǎn)�,技術(shù)路線分化(PowerVia低成本vs背面接觸微縮)��、良率優(yōu)化及多技術(shù)協(xié)同(GAAFET+3D堆疊)成競爭焦點(diǎn)�����。隨著工藝優(yōu)化,BSPDN將突破供電架構(gòu)限制��,成為AI�����、HPC芯片的核心技術(shù)支柱����。

趨勢二:2nm全面上量,GAAFET接棒FinFET

作者:黃燁鋒

自2021年IBM首度宣布造出2nm節(jié)點(diǎn)GAAFET晶體管�����,2nm工藝的熱議就開始了��。2021-2022年期間���,英特爾代工��、三星代工�����、臺積電(TSMC)相繼宣布了各自的2nm節(jié)點(diǎn)��,基本都明確會在2025年實(shí)現(xiàn)量產(chǎn)����。

從IEDM 2024大會上公布的數(shù)據(jù)來看,臺積電N2工藝持續(xù)在晶體管密度上領(lǐng)銜��,可達(dá)313MTr/mm²�,而目前已知三星SF2、英特爾18A工藝的數(shù)字是231與238�。雖然目前還沒有這些工藝的物理尺寸數(shù)據(jù),不過基于2021年IEEE發(fā)布的國際器件與系統(tǒng)路標(biāo)更新�����,“2.1nm節(jié)點(diǎn)”預(yù)期實(shí)現(xiàn)的接觸柵極間距(CGP)為45nm�,而最小金屬間距(MMP)在20nm左右�����。另外�,2021年IBM宣布的2nm晶體管柵極長度為12nm。

從FinFET走向GAAFET(來源:Intel)

無一例外���,幾家主要晶圓代工廠的2nm節(jié)點(diǎn)都會采用GAAFET結(jié)構(gòu)���,不再采用FinFET——所謂的納米片電流通道被橫置��,并被柵極四面環(huán)繞����。GAAFET作為被廣泛研究的新型器件結(jié)構(gòu)���,不僅實(shí)現(xiàn)了更好的溝道控制�,而且若對納米片的寬度與層數(shù)進(jìn)行調(diào)節(jié)���,搭配不同工作電壓與閾值��,還能在同一工藝平臺衍生出多種優(yōu)化方向的晶體管規(guī)格���,為芯片設(shè)計(jì)客戶提供更高的設(shè)計(jì)自由度,包括高性能與低功耗選擇��。

三家代工廠對GAAFET的稱呼各有不同:三星稱其為MBCFET���,臺積電稱其GAAFET���,英特爾的版本叫RibbonFET����。具體實(shí)施方案皆有差異���。雖說三星早在3nm節(jié)點(diǎn)就率先用上了GAAFET�,但應(yīng)用范圍與量產(chǎn)數(shù)量都極其有限�����,因此2026年2nm工藝芯片有望全面應(yīng)用于手機(jī)��、PC與HPC領(lǐng)域���,GAAFET也將全面在尖端工藝中實(shí)現(xiàn)對FinFET的接棒。

三家代工廠的2nm工藝應(yīng)當(dāng)都已經(jīng)進(jìn)入產(chǎn)能爬坡階段��。2025年10月�,英特爾率先發(fā)布了預(yù)計(jì)在2026年初問世、用于PC筆記本的Panther Lake處理器和用于數(shù)據(jù)中心服務(wù)器的Clearwater Forest處理器���,都將采用英特爾18A工藝���。

11月份�����,相關(guān)采用2nm工藝的三星Exynos 2600芯片單核性能超越蘋果M5的消息也開始刷屏……雖然截至發(fā)稿前尚無任何2nm芯片的確切性能與功耗數(shù)據(jù)����,這些信息的放出卻也表明英特爾和三星都有意在2nm GAAFET工藝節(jié)點(diǎn)上����,更積極地與臺積電一較高下。

趨勢三:CPO邁過發(fā)展拐點(diǎn)

作者:黃燁鋒

AI數(shù)據(jù)中心基于光互連本身并不稀奇�,但相較于可插拔光模塊,直接將實(shí)現(xiàn)光電轉(zhuǎn)換的硅光引擎和數(shù)字芯片封裝到一起���,即所謂的CPO技術(shù)�,能夠大幅提升互聯(lián)帶寬���、降低傳輸延遲���。

2025年的GTC活動上,英偉達(dá)發(fā)布NVIDIA Photonics芯片就是將交換芯片和硅光引擎封裝在了一起,帶來了3.5倍的能效提升��,10倍的抗干擾����、抗打斷能力,還更容易部署��,只需要以往1/4的激光器�,大幅降低了功耗和數(shù)據(jù)中心的總擁有成本(TCO)。

同一時(shí)間內(nèi)�,光通信巨頭、芯片制造商�����、云服務(wù)供應(yīng)商企業(yè)都相繼在CPO技術(shù)方向上下場與投入�����。CPO對于未來的AI數(shù)據(jù)中心�����,尤其在超節(jié)點(diǎn)�、萬卡集群十分流行的當(dāng)下,顯得格外重要:在AI大模型算力競賽�����、功耗問題越來越敏感的背景下自然成為香餑餑�。

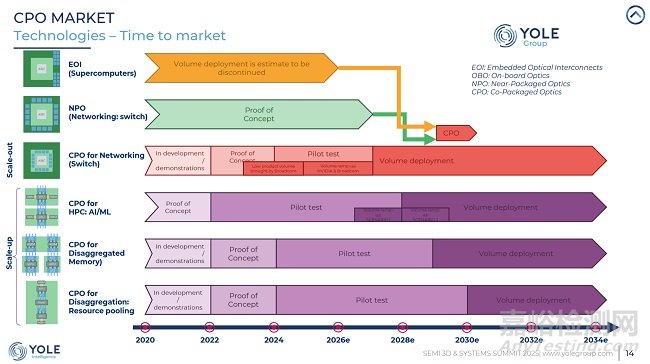

多家研究機(jī)構(gòu)的市場展望中都提到2025、2026年會成為CPO芯片發(fā)展的拐點(diǎn):尤其從試驗(yàn)性質(zhì)的部署�����、概念驗(yàn)證(PoC)�,開始走向試運(yùn)行、早期上量和采用率的提升�����,尤其是在超級集群之中���。不同互操作性標(biāo)準(zhǔn)的完善���、先進(jìn)封裝技術(shù)的完善也在加速CPO技術(shù)的落地。

2020-2034年CPO市場規(guī)模預(yù)測(來源:Yole Group)

更長遠(yuǎn)來看�,Yole Intelligence的數(shù)據(jù)顯示CPO市場的整體營收將從2024年的4,600萬美元,走向2030年的54億美元�����,年復(fù)合增長率(CAGR)達(dá)到了驚人的121%——Yole的這份數(shù)據(jù)可能在不同時(shí)期有所調(diào)整,但三位數(shù)的年復(fù)合增長率基本是明確的�����。

另外���,CPO在中國市場的發(fā)展尤為值得一提���。包括曦智科技在內(nèi)的國產(chǎn)CPO芯片企業(yè)認(rèn)為,受到貿(mào)易摩擦和技術(shù)封鎖的影響��,中國在構(gòu)建高算力AI芯片���、打造AI計(jì)算超節(jié)點(diǎn)及大規(guī)模訓(xùn)練集群的能力上因此受限�。

基于CPO的光互連能夠提升跨機(jī)柜���、節(jié)點(diǎn)的通信能力�����。在未來走向GPU或AI芯片直出光信號以后�,CPO技術(shù)有望緩解單位芯片AI算力不足、超節(jié)點(diǎn)構(gòu)建受限帶來的不良影響��。而且�����,硅光產(chǎn)品及CPO封裝并不特別依賴尖端制造工藝��,國內(nèi)頭部產(chǎn)線也具備出色的生產(chǎn)能力�����,產(chǎn)業(yè)鏈發(fā)展也相對健全��。因此���,硅光技術(shù)對中國的AI技術(shù)設(shè)施建設(shè)尤為重要。

從各個(gè)角度來看�����,CPO及未來的3D CPO都成為了AI技術(shù)發(fā)展路線上的必選項(xiàng)����。

趨勢四:RISC-V劍指全球算力“第三極”

作者:邵樂峰

從目前產(chǎn)業(yè)界釋放的信號看���,2026年將成為RISC-V關(guān)鍵技術(shù)產(chǎn)業(yè)化的重要節(jié)點(diǎn)。屆時(shí)�,RISC-V架構(gòu)將有望圍繞“行業(yè)專用化、高性能AI化��、生態(tài)工業(yè)化”三條主線����,聚焦六大核心看點(diǎn),快速成為除x86��、Arm之外全球算力“第三極”����。

技術(shù)上,RVA23服務(wù)器級配置文件將啟動早期部署�。2028年,下一代RVA30或?qū)⒔y(tǒng)一矩陣��、向量與張量三大AI擴(kuò)展�,形成與Armv9、x86-SSE同等完備且免授權(quán)費(fèi)的指令矩陣���。工藝端���,因先進(jìn)工藝逼近物理極限�����,Chiplet成為性能躍升的最佳捷徑,“通用RISC-V架構(gòu)+AI加速+I/O接口”的三明治結(jié)構(gòu)將更受行業(yè)青睞�。

伴隨著生成式AI推理需求爆發(fā),RISC-V未來演進(jìn)將聚焦兩個(gè)關(guān)鍵方向:一是推動向量處理單元(VPU)與張量處理單元(TPU)的深度融合��,實(shí)現(xiàn)通用并行計(jì)算能力與專用AI算力的高效協(xié)同�;二是通過動態(tài)電壓調(diào)節(jié)、指令集裁剪等技術(shù)手段���,進(jìn)一步提升AI設(shè)備的續(xù)航能力�����。

2026年RISC-V在安全與標(biāo)準(zhǔn)化領(lǐng)域也將迎來突破:RVA23-Automotive規(guī)范文件將有望完成ISO 26262 ASIL-D與IEC 61508 SIL3雙認(rèn)證����,輕量級內(nèi)存標(biāo)記和能力硬件增強(qiáng)RISC指令(CHERI)等硬件級安全機(jī)制也有望獲得通過���。目前�,RVA23文件規(guī)范已經(jīng)整合了81項(xiàng)擴(kuò)展標(biāo)準(zhǔn)�,明確了64位通用計(jì)算平臺的接口技術(shù)要求。接下來�����,向量擴(kuò)展2.0�、安全擴(kuò)展1.1等關(guān)鍵技術(shù)標(biāo)準(zhǔn)將完成修訂工作,進(jìn)一步降低技術(shù)開發(fā)門檻�����。

此外�����,地緣政治加速格局分化���,中國�����、印度����、歐洲中小廠商更多轉(zhuǎn)向開源指令集。2031年預(yù)計(jì)RISC-V SoC芯片出貨量將達(dá)200億顆�����,并在SoC市場獲得超過25%的滲透率�����。與此同時(shí)�����,RISC-V在消費(fèi)�、計(jì)算機(jī)�、汽車、數(shù)據(jù)中心���、工業(yè)����、網(wǎng)絡(luò)六大市場的份額會位于26%-39%之間��。

總體來看,未來3-5年內(nèi)�,RISC-V將通過面向汽車、AIoT�����、數(shù)據(jù)中心��、工業(yè)控制等場景發(fā)布的專用配置規(guī)范文件����,以“分層規(guī)范+兼容性認(rèn)證”規(guī)避碎片化問題,一邊沖擊服務(wù)器與PC級通用算力����,一邊疊加AI功能擴(kuò)展,在搶占AI推理����、自動駕駛、服務(wù)器等高增長市場的同時(shí)�����,逐步降低架構(gòu)遷移成本����。

趨勢五:Chiplet標(biāo)準(zhǔn)化浪潮重塑芯片設(shè)計(jì)新范式

作者:謝宇恒

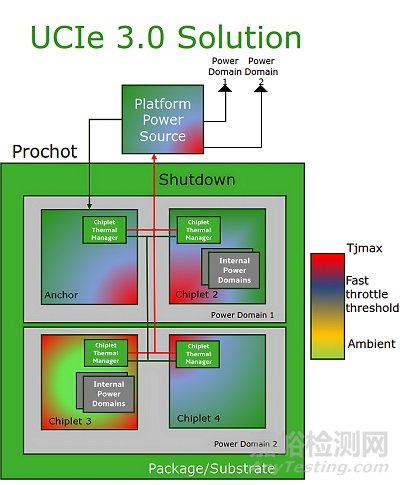

當(dāng)下摩爾定律逐漸觸及物理極限����,Chiplet技術(shù)已從“過渡之策”華麗轉(zhuǎn)身為“核心戰(zhàn)略”�。過去,它多被視為普通廠商應(yīng)對大芯片良率與成本難題的權(quán)宜之計(jì)�����;如今�����,隨著UCIe 2.0/3.0標(biāo)準(zhǔn)的確立�,Chiplet邁入了標(biāo)準(zhǔn)化爆發(fā)期�����,從少部分企業(yè)的內(nèi)部優(yōu)化策略����,躍升為全行業(yè)共同遵循的接口與規(guī)則,推動著半導(dǎo)體產(chǎn)業(yè)架構(gòu)深度重構(gòu)���。

UCIe標(biāo)準(zhǔn)的演進(jìn)����,是Chiplet技術(shù)騰飛的關(guān)鍵引擎。1.0版本搭建起了Chiplet互連雛形����,但帶寬、延遲和協(xié)議兼容性短板明顯���。2.0/3.0版本則讓Chiplet互連步入實(shí)用階段��,更高的帶寬密度及更廣泛的協(xié)議支持�����,讓邏輯�����、存儲����、I/O乃至未來光子芯片能在同一封裝內(nèi)互聯(lián)���,這種跨工藝節(jié)點(diǎn)�����、跨功能模塊的集成方式���,正在重塑多個(gè)芯片設(shè)計(jì)的基本范式��。

UCIe 3.0新增功能(來源:UCIe聯(lián)盟)

設(shè)計(jì)模式上����,傳統(tǒng)單片SoC模式要求CPU芯片集成所有功能����,導(dǎo)致設(shè)計(jì)復(fù)雜度與制造成本不斷攀升,而Chiplet架構(gòu)支持不同模塊采用最適配工藝節(jié)點(diǎn)����,例如GPU邏輯用先進(jìn)工藝���,I/O與模擬電路則用成熟工藝��,可實(shí)現(xiàn)高效的資源利用��。產(chǎn)業(yè)分工方面���,UCIe標(biāo)準(zhǔn)推廣有望催生類似“IP核市場”的開放生態(tài)���,不同廠商提供標(biāo)準(zhǔn)化模塊,系統(tǒng)設(shè)計(jì)者則如拼積木般自由組合�����,這不僅優(yōu)化了產(chǎn)業(yè)分工�,還可能催生新的產(chǎn)業(yè)生態(tài)。

然而���,Chiplet技術(shù)發(fā)展并非一帆風(fēng)順�。3D堆疊與高密度互連普及�����,使功耗管理���、熱設(shè)計(jì)、信號完整性成為新瓶頸����。在AI大模型訓(xùn)練等極限算力場景下����,如何在有限封裝空間實(shí)現(xiàn)高帶寬�、低延遲且穩(wěn)定的性能,成為Chiplet普及的關(guān)鍵�����。同時(shí)�,安全性與數(shù)據(jù)一致性也需新的體系架構(gòu)來保障,以防止開放性帶來新的風(fēng)險(xiǎn)���。

展望未來����,Chiplet發(fā)展將呈階段性特征���。短期內(nèi)�,UCIe 2.0/3.0將推動HPC與AI芯片Chiplet化��,成為事實(shí)上的行業(yè)標(biāo)準(zhǔn)����;中期�,Chiplet將與光互連�、3D封裝深度融合,突破帶寬與能效瓶頸�;遠(yuǎn)期,Chiplet生態(tài)或轉(zhuǎn)變成一個(gè)開放的市場���,實(shí)現(xiàn)跨領(lǐng)域���、跨工藝互連?����?偠灾?����,目前Chiplet標(biāo)準(zhǔn)化的爆發(fā)�����,既是摩爾時(shí)代算力競賽的關(guān)鍵路徑,也是需求拉動下的產(chǎn)業(yè)變革���,誰能構(gòu)建最具活力的Chiplet生態(tài)�����,誰就能在后摩爾時(shí)代算力競賽中搶占先機(jī)�����。

趨勢六:芯片堆疊革命,混合鍵合開啟邏輯芯片3D時(shí)代

作者:趙明燦

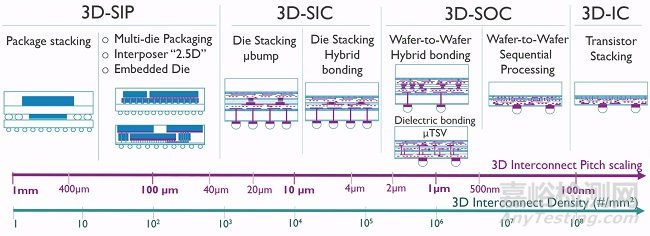

混合鍵合技術(shù)通過銅對銅直接鍵合突破傳統(tǒng)封裝極限�,已成為后摩爾時(shí)代邏輯芯片三維集成的核心方案�����。其介電層與金屬層同步鍵合���,可將互連間距壓縮至3μm以下,連接密度較傳統(tǒng)TSV技術(shù)提升10-100倍�����,為邏輯與存儲的異構(gòu)集成提供原子級互聯(lián)能力����。

3D互連格局��。(來源:imec)

該技術(shù)核心突破在于無凸點(diǎn)互連架構(gòu)���,通過三大工藝實(shí)現(xiàn):在表面工程方面�,采用化學(xué)機(jī)械拋光(CMP)將銅墊凹陷控制在2.5nm以內(nèi)�����,結(jié)合等離子切割實(shí)現(xiàn)無顆粒邊緣�����,確保原子級平整接觸����;在對準(zhǔn)技術(shù)方面,芯片對晶圓(D2W)鍵合套刻誤差小于350nm�����,晶圓對晶圓(W2W)鍵合良率達(dá)99.9%,有效支撐3D NAND的超高層堆疊��;在鍵合機(jī)制方面���,在300-400℃低溫下通過熱壓合實(shí)現(xiàn)銅原子擴(kuò)散焊接�,同時(shí)介電層發(fā)生分子鍵合���,形成兼具機(jī)械強(qiáng)度與電學(xué)性能的穩(wěn)定復(fù)合界面�����。

2025年�,行業(yè)呈現(xiàn)技術(shù)分化與協(xié)同并存格局���。臺積電SoIC-X技術(shù)以9μm間距支撐AMD MI300系列,接點(diǎn)密度提升15倍����;其SoIC-P方案(6μm間距)面向中低端市場,2025年量產(chǎn)N3-on-N4堆疊�����,良率損失控制在5%以下。英特爾Foveros Direct技術(shù)通過銅對銅混合鍵合接口實(shí)現(xiàn)小于5μm的互連間距���,后續(xù)18A-PT工藝將與14A節(jié)點(diǎn)(基于High-NA EUV)結(jié)合��。三星X-Cube技術(shù)采用TSV與混合鍵合融合架構(gòu)����,為16層HBM4E開發(fā)4μm間距方案�,可在775μm模塊高度內(nèi)將芯片數(shù)量從12層增至17層(含1顆基礎(chǔ)芯片)���。

前沿研發(fā)方面����,imec已成功驗(yàn)證2μm間距D2W鍵合�����,Kelvin結(jié)構(gòu)電學(xué)良率超過85%�����;SK海力士在HBM5開發(fā)中證實(shí),混合鍵合是實(shí)現(xiàn)20層堆疊(單芯片厚度20μm)的唯一可行路徑�。

展望2026年,邏輯芯片3D化將迎來三大技術(shù)躍遷�����。在間距突破方面���,臺積電A16節(jié)點(diǎn)(1.6nm工藝)將結(jié)合背面供電(SPR)與混合鍵合���,通過信號層與電源層分離布線,在3μm間距下實(shí)現(xiàn)104/mm2連接密度���,較2025年提升3倍���;英特爾第二代Foveros Direct目標(biāo)間距2μm,計(jì)劃集成光互連引擎�,實(shí)現(xiàn)片間1.6Tb/s光學(xué)帶寬。在工藝融合方面�,CoWoS與SoIC的3.5D+3D混合架構(gòu)將成為主流,臺積電CoWoS CPO方案通過光引擎整合���,可降低功耗50%����、減少延遲10倍;EMIB與Foveros Direct協(xié)同封裝則支持5×5處理器陣列�����,每邊帶寬達(dá)4.5Tbps���。在良率控制方面��,通過已知合格裸片(KGD)篩選與集體D2W鍵合優(yōu)化���,邏輯芯片堆疊良率損失有望從當(dāng)前15%降至8%以下���。

趨勢七:HBM4量產(chǎn)引領(lǐng)算存架構(gòu)革新

作者:吳清珍

2026年�,高帶寬內(nèi)存市場將迎來新的拐點(diǎn)�。在數(shù)據(jù)中心和HPC持續(xù)擴(kuò)容的背景下,算力架構(gòu)對帶寬�����、容量與延遲的要求被不斷抬升���,傳統(tǒng)顯存模式在資源利用和跨節(jié)點(diǎn)訪問方面的限制愈發(fā)明顯�。在這樣的趨勢下,HBM4的商業(yè)化量產(chǎn)將逐漸確立其行業(yè)地位�,成為產(chǎn)業(yè)鏈關(guān)注的核心。

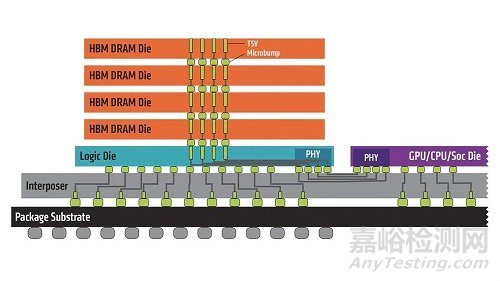

HBM內(nèi)部結(jié)構(gòu)(來源:AMD)

HBM4的接口位寬加倍至2048位�,使單堆棧帶寬高達(dá)2TB/s。通過先進(jìn)的3D堆疊技術(shù)�����,它實(shí)現(xiàn)了最高64GB的單堆棧容量�����,并優(yōu)化了信號傳輸和功耗����,以滿足AI和HPC對數(shù)據(jù)處理的需求。

在量產(chǎn)進(jìn)度上����,頭部廠商已展開競速。SK海力士在2025年完成HBM4開發(fā)并開始小批出貨�����,計(jì)劃2026年擴(kuò)大生產(chǎn)。三星和美光也將陸續(xù)進(jìn)入量產(chǎn)階段����。臺積電通過提升CoWoS產(chǎn)能和優(yōu)化封裝流程,為HBM4的高密度集成提供基礎(chǔ)支持��。整體產(chǎn)業(yè)鏈正在形成協(xié)同����,加速落地。

為適配更高帶寬密度���,封裝技術(shù)將同步演進(jìn)�。CoWoS將進(jìn)一步提升布線能力��,玻璃襯底等下一代封裝方案將加速驗(yàn)證�,以提供更低熱膨脹系數(shù)與更高互連密度��。Chiplet架構(gòu)將與HBM4綁定����,而硅光互連可能在極限帶寬場景中進(jìn)行小規(guī)模測試,以緩解銅互連在高頻長距條件下的損耗與衰減���。

值得關(guān)注的是HBM與CXL的協(xié)同�。借助CXL 3.0,不同加速器�、CPU以及專用處理單元可以與更大的內(nèi)存資源池建立高速連接。HBM作為加速器近鄰高帶寬內(nèi)存�,與通過CXL擴(kuò)展的通用內(nèi)存池協(xié)同工作,能在訓(xùn)練峰值時(shí)動態(tài)申請連續(xù)空間����,在推理階段靈活分配小塊資源,提升整體利用率�,減少碎片化并降低通信開銷。

從演進(jìn)路線來看���,HBM4并非終點(diǎn)���。更高帶寬密度的HBM4e已在規(guī)劃中,HBM5的研發(fā)也已啟動����,將在接口速率與堆疊高度方面繼續(xù)突破。玻璃襯底�、硅光互連以及更先進(jìn)的熱管理方法都將持續(xù)完善。

面向2026年,HBM4的量產(chǎn)不僅是性能升級���,更是圍繞封裝���、互連、調(diào)度與資源組織方式的系統(tǒng)性演進(jìn)����。在計(jì)算架構(gòu)從板卡級走向集群級的過程中,高帶寬存儲將成為不可或缺的基礎(chǔ)能力��,并在未來數(shù)年持續(xù)影響產(chǎn)業(yè)節(jié)奏���。

趨勢八:第三代半導(dǎo)體驅(qū)動綠色未來

作者:Anthea Chuang

隨著全球能源轉(zhuǎn)型和AI算力需求的爆發(fā)式增長���,以碳化硅(SiC)和氮化鎵(GaN)為代表的寬禁帶(WBG)半導(dǎo)體,已從利基市場邁向主流應(yīng)用�。到2026年,第三代半導(dǎo)體的發(fā)展重點(diǎn)將不再局限于單一器件性能的提升�����,而是聚焦于規(guī)?;a(chǎn)、系統(tǒng)級集成與高可靠性����,以全面滿足電動汽車、超快充�、可再生能源及AI數(shù)據(jù)中心對高效率、低能耗與低碳排放的極致需求�����。

在高集成度與系統(tǒng)級芯片方面�����,WBG功率器件正加速從傳統(tǒng)分立器件向模塊化與片上集成演進(jìn)�����。此外��,通過3D堆疊與Chiplet技術(shù),可有效縮短功率傳輸路徑、降低寄生電感并改善熱阻,而垂直堆疊也開始在正在挑戰(zhàn)高壓領(lǐng)域的GaN功率器件中崛起����。

垂直結(jié)構(gòu)氮化鎵器件正逐步實(shí)現(xiàn)商業(yè)化���。進(jìn)入2026年���,氮化鎵發(fā)展的關(guān)鍵在于硅基氮化鎵技術(shù)的持續(xù)優(yōu)化,以確保在標(biāo)準(zhǔn)硅工藝生產(chǎn)線上制造出具備高可靠性且成本更具競爭力的器件�。

在高耐壓領(lǐng)域,碳化硅在1200V電壓等級仍具優(yōu)勢����。預(yù)計(jì)2026年,電動汽車制造商將加速導(dǎo)入800V高壓電池平臺�����,直接拉動對1200V乃至1700V碳化硅功率模塊的需求���。

2026年��,異質(zhì)外延技術(shù)將成為降低成本的核心路徑之一����,特別是針對高頻應(yīng)用的高電子遷移率晶體管(HEMT)結(jié)構(gòu)的優(yōu)化���。通過在硅或SiC襯底上外延生長GaN層�,可在性能與制造成本之間取得更好平衡��。近期研究更嘗試采用石墨烯與六方氮化硼(h-BN)等二維材料作為緩沖層,以緩解晶格失配并提升散熱性能���,推動300mm大尺寸晶圓工藝走向成熟��。

高導(dǎo)熱封裝與模塊化集成技術(shù)也將在2026年成為廠商競爭焦點(diǎn)���。新一代封裝將采用銅夾����、燒結(jié)銀等低熱阻互連材料�����,以及直接鍵合襯底與嵌入式芯片設(shè)計(jì)�����,顯著提升熱管理能力與系統(tǒng)可靠性����。此外���,先進(jìn)功率模塊技術(shù)也將成為發(fā)展重點(diǎn)�����,通過平面化設(shè)計(jì)�����、雙面散熱或直接液冷等方案���,使功率模塊在更緊湊的空間內(nèi)處理更高功率,實(shí)現(xiàn)低熱阻�、高散熱性能與高功率密度的統(tǒng)一目標(biāo)�。

趨勢九:AI加持EDA�����,驅(qū)動芯片設(shè)計(jì)“左移”

作者:Susan Hong

隨著人工智能深度融入半導(dǎo)體產(chǎn)業(yè)��,電子設(shè)計(jì)自動化(EDA)正加速從傳統(tǒng)的“輔助工具”轉(zhuǎn)型為“智能決策引擎”�。這一變革的核心是“設(shè)計(jì)左移”(Shift Left)�,即將原本位于芯片開發(fā)后期的性能分析、功耗預(yù)測與可靠性驗(yàn)證提前至設(shè)計(jì)初期��,使團(tuán)隊(duì)能夠更早發(fā)現(xiàn)問題����、優(yōu)化方案,從而縮短開發(fā)周期并降低重新流片(respin)風(fēng)險(xiǎn)�����。

“設(shè)計(jì)左移”并非全新概念���,但AI的引入加速了其從理念走向?qū)嵺`�����。借助機(jī)器學(xué)習(xí)與強(qiáng)化學(xué)習(xí)�����,AI可在設(shè)計(jì)早期預(yù)測芯片的PPA����,并實(shí)時(shí)提供優(yōu)化建議,幫助工程師在RTL階段即鎖定最優(yōu)架構(gòu)���。這不僅提升了設(shè)計(jì)效率��,也推動芯片開發(fā)從經(jīng)驗(yàn)驅(qū)動轉(zhuǎn)向數(shù)據(jù)驅(qū)動的智能化模式����。

全球三大EDA廠商正引領(lǐng)這一轉(zhuǎn)型�����。新思科技(Synopsys)率先以“設(shè)計(jì)左移”為核心戰(zhàn)略���,如今更將AI前置至設(shè)計(jì)初期�,加速仿真與設(shè)計(jì)探索�,使EDA工具升級為智能協(xié)同平臺����;面對汽車電子數(shù)字化的挑戰(zhàn)�����,公司還提出“三重左移”(Triple Shift Left)策略�����,將傳統(tǒng)串行開發(fā)流程轉(zhuǎn)變?yōu)椴⑿袇f(xié)同�,并結(jié)合虛擬原型實(shí)現(xiàn)更早期的功能與安全驗(yàn)證��。

楷登電子(Cadence)則聚焦驗(yàn)證革新����。其臺灣區(qū)總經(jīng)理宋栢安指出:“在AI時(shí)代,驗(yàn)證的重要性甚至超過設(shè)計(jì)本身�����。”AI讓驗(yàn)證更早介入設(shè)計(jì)階段�����,通過自動生成測試、實(shí)時(shí)異常檢測與軟硬件協(xié)同仿真�,大幅縮短開發(fā)周期,實(shí)現(xiàn)設(shè)計(jì)與驗(yàn)證同步�。

西門子EDA資深總監(jiān)Sathishkumar Balasubramanian認(rèn)為,AI在EDA的價(jià)值不僅是概念�����,而是通過工具�����、流程與平臺三方面落地真正的“Shift Left”���。借助數(shù)字孿生����,設(shè)計(jì)團(tuán)隊(duì)可在芯片開發(fā)初期進(jìn)行全面分析與優(yōu)化���,進(jìn)一步提升效率與設(shè)計(jì)質(zhì)量�����。

以AI推動設(shè)計(jì)左移:AI正成為EDA流程優(yōu)化的核心動力���,使設(shè)計(jì)團(tuán)隊(duì)在更早階段完成優(yōu)化與驗(yàn)證����,加速開發(fā)與創(chuàng)新�����。(來源:西門子EDA)

展望2026年�����,EDA將邁入“多智能體AI”(Multi-Agent AI)新階段�����。多個(gè)AI智能體將在設(shè)計(jì)流程中分工協(xié)作���,從規(guī)格生成到簽核分析自動銜接,形成具自我學(xué)習(xí)與協(xié)同決策能力的智能設(shè)計(jì)網(wǎng)絡(luò)��。這將進(jìn)一步提升設(shè)計(jì)靈活性與自動化深度�����,推動EDA從“輔助設(shè)計(jì)”邁向“共創(chuàng)設(shè)計(jì)”,并推動芯片開發(fā)更具預(yù)測性與智能化�,成為半導(dǎo)體創(chuàng)新的關(guān)鍵力量。

趨勢十:存算一體技術(shù)加速落地

作者:劉于葦

存算一體技術(shù)作為突破馮·諾依曼架構(gòu)瓶頸的關(guān)鍵路徑����,將在2026年加速從技術(shù)驗(yàn)證走向規(guī)模化商用�。該技術(shù)通過將計(jì)算單元嵌入存儲器內(nèi)部,消除傳統(tǒng)架構(gòu)中“存儲墻”與“功耗墻”導(dǎo)致的90%以上數(shù)據(jù)搬運(yùn)能耗��,理論上可實(shí)現(xiàn)10-100TOPS/W的能效比�,成為繼CPU、GPU之后的算力第三極���。當(dāng)前技術(shù)路徑已形成近存計(jì)算(如AMD Zen系列CPU的HBM共封裝)���、存內(nèi)處理(三星HBM-PIM)和存內(nèi)計(jì)算(CIM)三大方向,其中存內(nèi)計(jì)算因徹底融合存儲與計(jì)算�����,被視為最具顛覆性的技術(shù)路線�����。

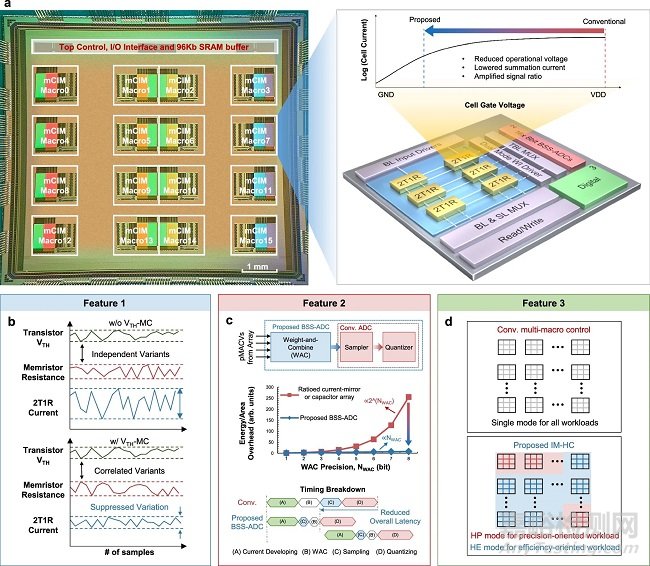

2025年是存算一體技術(shù)突破的關(guān)鍵節(jié)點(diǎn)。北京大學(xué)團(tuán)隊(duì)基于憶阻器構(gòu)建的存算一體排序架構(gòu)�,通過“無比較器”設(shè)計(jì)實(shí)現(xiàn)15倍速度提升、160倍能效提升及32倍面積效率提升�����,并驗(yàn)證了在路徑規(guī)劃�、神經(jīng)網(wǎng)絡(luò)推理等場景的實(shí)用性。南京大學(xué)團(tuán)隊(duì)提出基于器件幾何比例的模擬存內(nèi)計(jì)算方案�����,在180nm CMOS工藝下實(shí)現(xiàn)0.101%的均方根誤差���,且在-78.5℃至180℃極端環(huán)境下保持穩(wěn)定,刷新模擬計(jì)算精度紀(jì)錄�����。中國科學(xué)院微電子研究所的近閾值RRAM存算一體芯片�����,通過2T1R單元和電荷堆疊技術(shù)實(shí)現(xiàn)256通道并行計(jì)算,能效達(dá)55.21-88.51TOPS/W��,為邊緣AI提供高能效解決方案��。

基于近閾值計(jì)算的RRAM存算一體芯片(來源:中科院微電子所)

產(chǎn)業(yè)競爭格局方面���,海外廠商以近存計(jì)算為切入點(diǎn)快速落地����。英偉達(dá)�、三星、英特爾通過HBM共封裝技術(shù)推動近存計(jì)算在數(shù)據(jù)中心的應(yīng)用�,而d-Matrix的Corsair芯片則集成大容量SRAM與LPDDR5X,將推理任務(wù)能耗降低70%以上�����。國內(nèi)企業(yè)方面,后摩智能發(fā)布160TOPS算力的SRAM存算一體智駕芯片�,知存科技量產(chǎn)全球首款NOR Flash存算一體語音芯片,昕原半導(dǎo)體則實(shí)現(xiàn)28nm ReRAM芯片量產(chǎn)�。

2026年,預(yù)計(jì)存算一體技術(shù)將呈現(xiàn)三大趨勢:一是技術(shù)路徑分化�,近存計(jì)算憑借低成本優(yōu)勢主導(dǎo)端側(cè)市場,憶阻器�、RRAM、SRAM等存內(nèi)計(jì)算依托極致能效比搶占云端AI推理份額����;二是生態(tài)協(xié)同加速,器件-電路-系統(tǒng)級技術(shù)棧整合成為關(guān)鍵��;三是應(yīng)用場景向自動駕駛���、智慧醫(yī)療等實(shí)時(shí)性要求高的領(lǐng)域拓展�。