摘要

隨著高性能AI設(shè)計需求的增長�,處理器需要更高的引腳數(shù)量、更密集的布局和更快的IO通道�。這些要求對高速信號從CPU或GPU引腳區(qū)域的引出(breakout)提出了挑戰(zhàn)�,導(dǎo)致引出線更長�、布線更密集、信號間距更小�,以及走線常常沿著反焊盤(antipad)邊緣布線。PCB制造工藝的變異�,例如層與層之間的對位偏差、鉆孔和蝕刻不一致�,可能導(dǎo)致高速走線的部分區(qū)域暴露在反焊盤區(qū)域,顯著降低串?dāng)_性能�。本文報告了廣泛的測量和電氣仿真,以識別影響串?dāng)_的關(guān)鍵因素�。最后,高分辨率3D X射線分析揭示了制造后引腳區(qū)域布線的實(shí)際情況�。

1. 引言

隨著對高性能AI設(shè)計需求的增長,處理器需要更高的引腳數(shù)量以及更多�、更密集、更快的IO通道�。這導(dǎo)致在CPU或GPU引腳區(qū)域周圍,高速差分信號的引出布線面臨更復(fù)雜的挑戰(zhàn)�。這些挑戰(zhàn)包括更長的引出長度、更緊湊的布線�、與相鄰信號間距的減小,以及走線常??拷春副P邊緣。隨著數(shù)據(jù)速率進(jìn)一步提高�,在引腳區(qū)域維持可接受的串?dāng)_水平并最小化阻抗不連續(xù)性變得日益關(guān)鍵且充滿挑戰(zhàn)�。

基于設(shè)計的幾何形狀�,已有各種技術(shù)被探索用于減少引腳區(qū)域的串?dāng)_[1][2][3]。然而�,仿真與基于實(shí)際制造幾何形狀和疊層的測量之間的相關(guān)性可能尚未得到充分解決或分析。由于制造變異�,串?dāng)_水平可能顯著惡化。由于串?dāng)_也會受到PCB材料特性(如介電常數(shù)Er)的影響�,本研究通過構(gòu)建大量采用不同PCB材料的電氣測試載體來調(diào)查這一現(xiàn)象。我們選擇了四家PCB供應(yīng)商�,每家提供五種不同的材料,并對每種材料的多個面板進(jìn)行了研究�。這種方法使得測量和仿真之間能夠建立關(guān)聯(lián),從而對不同PCB材料特性進(jìn)行敏感性研究�。使用理想走線和疊層幾何形狀的初始仿真顯示與測量結(jié)果相關(guān)性差,這促使我們進(jìn)行更深入的調(diào)查�。本文介紹了以下關(guān)鍵研究:

1.PCB材料特性變異影響的建模和仿真研究。

2.影響串?dāng)_的制造和設(shè)計因素分析�,包括:反焊盤尺寸;差分對走線之間的對位偏差�;在層對位偏差下,沿引出走線的周期性反焊盤數(shù)量�;在層對位偏差下,沿引出走線的周期性反焊盤尺寸

3.測試樣品的高分辨率3D X射線分析�,以檢查制造后的實(shí)際引腳區(qū)域幾何形狀,支持仿真和測量結(jié)果。

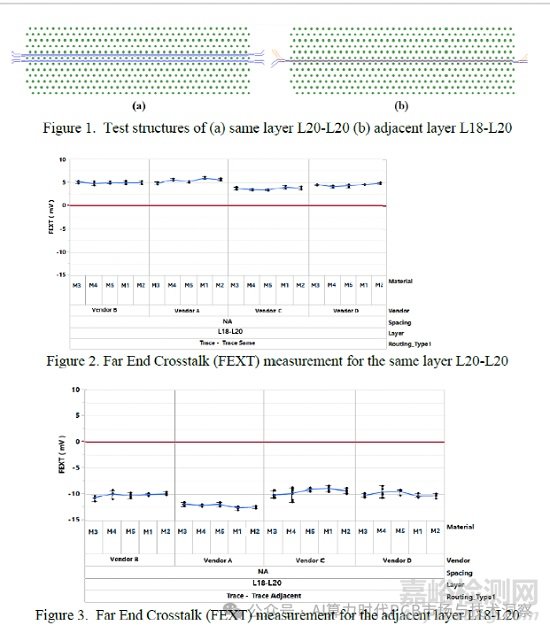

2. 串?dāng)_分析

隨著信號速度的提高�,超低損耗PCB材料已被廣泛采用�。在本研究中,測試PCB由四家PCB供應(yīng)商(A�、B、C�、D)和五種不同材料(M1、M2�、M3、M4�、M5)制造,采用為數(shù)據(jù)中心系統(tǒng)設(shè)計的高性能22層PCB疊層�。選擇差分對的引出走線寬度和間距以適應(yīng)引腳區(qū)域,并進(jìn)一步調(diào)整以優(yōu)化阻抗并盡可能減少串?dāng)_�。疊層設(shè)計包括4密耳的核心層和5密耳的半固化片。測試結(jié)構(gòu)如圖1所示�,包括(a)同層(L20-L20)和(b)相鄰層(L18-L20)。研究重點(diǎn)在于遠(yuǎn)端串?dāng)_(FEXT)�,測量結(jié)果見圖2和圖3。差分串?dāng)_水平(單位為mV)基于VNA對3英寸長差分對差分走線耦合的測量計算�,使用15ps上升時間。采用了EUL測試結(jié)構(gòu)[4]�。

在測量中,所有測試板上都一致觀察到相鄰層上的高串?dāng)_�。然而,使用全波3D工具和理想走線幾何形狀及PCB疊層的初始仿真串?dāng)_與測量結(jié)果相關(guān)性不佳。對于同層(L20-L20)�,初始仿真顯示約1.9 mV的串?dāng)_,而測量值平均在4-5 mV左右�。對于相鄰層(L18-L20),初始仿真顯示約4.5 mV的串?dāng)_�,而測量值平均在8-12 mV之間。這些測量與仿真之間的顯著差異促使我們進(jìn)行進(jìn)一步調(diào)查�。

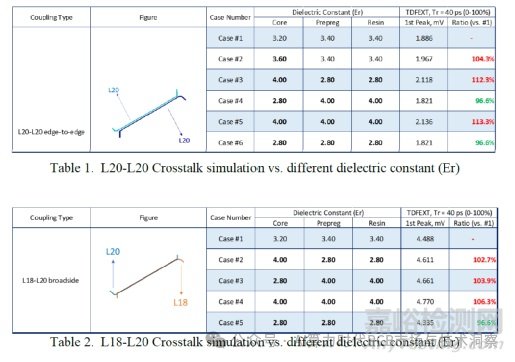

2.1 介電常數(shù)變異研究

為了使仿真結(jié)果與測量結(jié)果一致,第一個調(diào)整是改變CPU引腳區(qū)域中核心層�、半固化片以及信號層周圍樹脂填充區(qū)的介電常數(shù)(Er)?;诒砀?和表格2的關(guān)鍵發(fā)現(xiàn)包括:

-更高的介電常數(shù)對應(yīng)更高的串?dāng)_。

-在介電常數(shù)范圍(2.8-4.0)內(nèi)�,串?dāng)_差異在7%以內(nèi),這不足以解釋測量中觀察到的增加�。

2.2 制造變異研究

為了解決仿真與測量之間的大幅差異,我們調(diào)查了幾種可能影響串?dāng)_的制造變異:

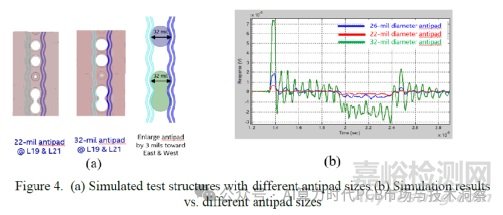

反焊盤尺寸

對22mil�、26mil(基線)和32mil的反焊盤尺寸進(jìn)行了仿真。圖4(a)顯示了仿真的測試結(jié)構(gòu)�,圖4(b)展示了結(jié)果。較大的反焊盤直徑對應(yīng)增加的串?dāng)_�。使用22mil反焊盤直徑時,串?dāng)_水平從1.9 mV降低到0.6 mV�,實(shí)現(xiàn)了約68%的降低。相反�,32mil的反焊盤直徑將串?dāng)_從1.9 mV增加到7.4 mV�,增長了約300%�。

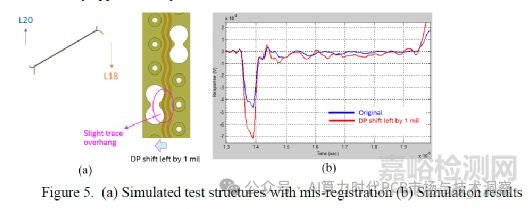

差分對走線之間的對位偏差

差分對由兩條走線DP和DN組成,并排布線�,每條走線承載等幅反向信號。圖5顯示了在仿真中將差分對的DP(差分對的左側(cè))向左移動1密耳的效果�。這種移動導(dǎo)致走線輕微懸垂在反焊盤上�,使串?dāng)_增加了約50%,從4.5 mV增加到7.1 mV�。

沿引出走線的周期性反焊盤數(shù)量

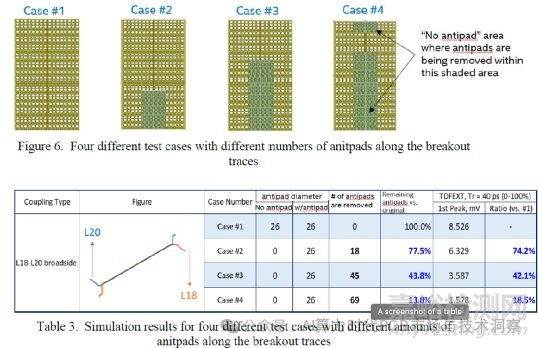

為了檢查反焊盤數(shù)量和相鄰GND層對位偏差對串?dāng)_的影響,仿真了四個測試案例(圖6)�。請注意,圖6中的引腳區(qū)域僅為示意�。案例#1作為基線,包含所有反焊盤�;案例#2中,移除了18個反焊盤(替換為GND)�;案例#3中,移除了45個反焊盤(替換為GND)�;案例#4中,移除了69個反焊盤(替換為GND)�。所有案例均假設(shè)有3密耳的層間對位偏差。如表3所示�,案例#2、#3和#4的串?dāng)_水平分別降低了74%�、42%和18%�。串?dāng)_的減少幾乎與移除的反焊盤數(shù)量成正比�。

沿引出走線的周期性反焊盤尺寸

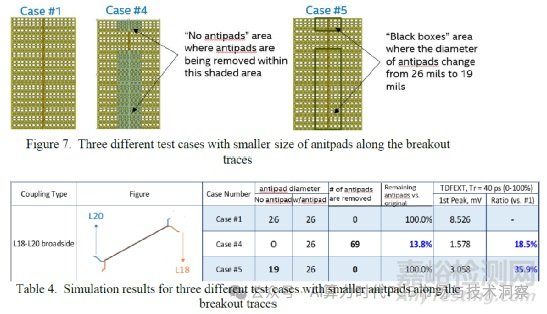

為了評估較小反焊盤與相鄰GND層對位偏差結(jié)合的效果,仿真了三個案例(圖7)�。案例#1是基線,所有反焊盤為26密耳�;案例#4移除了69個反焊盤(替換為GND);案例#5將案例#4中相同的69個反焊盤替換為19密耳反焊盤�,而非原來的26密耳。所有案例均有3密耳的層間對位偏差�。如表4所示,案例#4的串?dāng)_降低了18.5%�,案例#5降低了35.9%。由于在實(shí)際應(yīng)用中通常無法完全移除反焊盤�,案例#5模擬了引出走線遠(yuǎn)離反焊盤布線的情況。結(jié)果表明�,使引出走線遠(yuǎn)離反焊盤布線可以減少串?dāng)_,盡管減少不是線性的�。

基于以上分析,建議在設(shè)計和制造技術(shù)允許的范圍內(nèi)使用盡可能小的反焊盤�;布線時遠(yuǎn)離反焊盤(例如3-4mil)以適應(yīng)制造層對位偏差;并對于高速引腳區(qū)域布線�,盡可能保持引出長度最短。

3. 高分辨率3D X射線分析

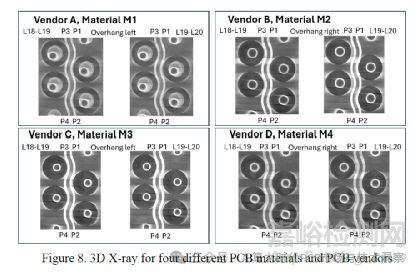

為了檢查PCB制造后的實(shí)際引腳區(qū)域幾何形狀�,對四個有代表性的測試樣品進(jìn)行了高分辨率3D X射線分析,每個樣品來自不同的PCB供應(yīng)商并使用超低損耗材料�。圖8顯示了四個樣品的3D X射線引腳區(qū)域幾何形狀以及相應(yīng)的單端測量結(jié)果(圖9)�。

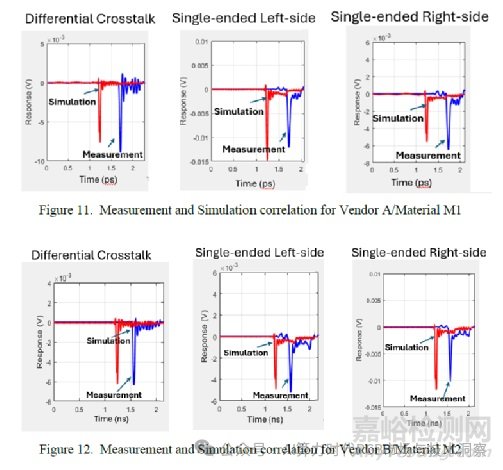

供應(yīng)商A 材料M1: 反焊盤尺寸比設(shè)計尺寸(26密耳)大約2密耳�。包括層間對位偏差和增大的反焊盤尺寸在內(nèi)的最終對位偏差,核心層為1.3密耳�,半固化片為1.8密耳。因此�,差分走線的左側(cè)暴露在反焊盤中,與測量結(jié)果中指示左側(cè)單端串?dāng)_占主導(dǎo)地位相符�。

供應(yīng)商B 材料M2: 反焊盤尺寸比設(shè)計大1.2密耳。包括層間對位偏差和增大的反焊盤尺寸在內(nèi)的最終對位偏差�,核心層為0.5密耳�,半固化片為2.33密耳。因此�,差分走線的右側(cè)暴露在反焊盤中,這與測量結(jié)果顯示右側(cè)單端串?dāng)_占主導(dǎo)地位一致�。

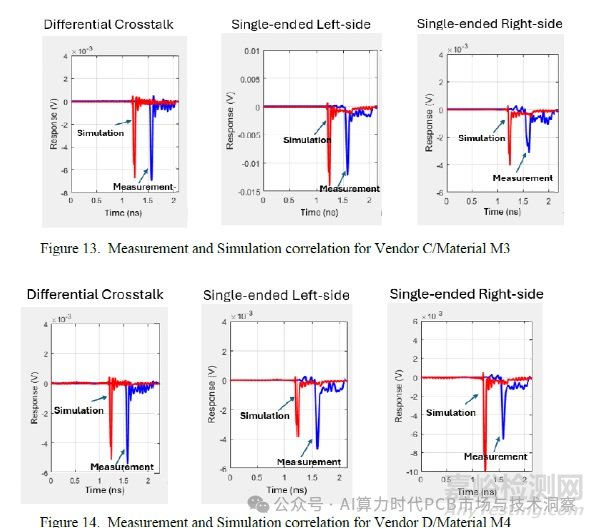

供應(yīng)商C 材料M3: 反焊盤尺寸比設(shè)計大0.9密耳。包括層間對位偏差和增大的反焊盤尺寸在內(nèi)的最終對位偏差�,核心層為1.11密耳,半固化片為1.95密耳�。因此,差分走線的左側(cè)暴露在反焊盤中�,與測量結(jié)果中指示左側(cè)單端串?dāng)_占主導(dǎo)地位一致。

供應(yīng)商D 材料M4: 反焊盤尺寸接近設(shè)計規(guī)格�。包括層間對位偏差和增大的反焊盤尺寸在內(nèi)的最終對位偏差,核心層為0.43密耳�,半固化片為1.43密耳�。因此�,差分走線的右側(cè)輕微暴露在反焊盤中,這與測量結(jié)果顯示右側(cè)單端串?dāng)_略微占主導(dǎo)地位相符�。

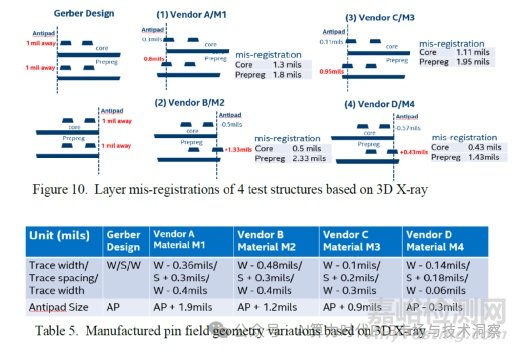

基于以上分析,我們可以確認(rèn)引腳區(qū)域串?dāng)_退化受到PCB制造變異的顯著影響�。此外,測量結(jié)果可以很容易地預(yù)測高速差分對的哪一側(cè)懸垂在反焊盤上�。圖10和表格5總結(jié)了通過3D X射線分析揭示的PCB制造后觀察到的層對位偏差和幾何形狀。

4.更新后的仿真與測量相關(guān)性

基于從圖10和表格5中獲得的關(guān)于層對位偏差和引腳區(qū)域幾何形狀的更新3D X射線數(shù)據(jù)�,進(jìn)行了更新后的仿真以與測量結(jié)果關(guān)聯(lián)。這里使用了40 ps上升時間的TDR�,但根據(jù)設(shè)計應(yīng)用和測量能力,也可以使用更快的上升時間�。如圖11至圖14所示,更新后的仿真與差分和單端串?dāng)_的測量結(jié)果均吻合良好�。

總結(jié)

本研究分析了由PCB制造變異引起的引腳區(qū)域串?dāng)_退化。通過廣泛的測量和電氣仿真來識別關(guān)鍵影響因素�。進(jìn)行了高分辨率3D X射線分析以揭示制造后的引腳區(qū)域布線情況。最終�,更新后的仿真顯示與測量結(jié)果具有良好的相關(guān)性。以下是要點(diǎn)總結(jié):

1.制造變異在引腳區(qū)域串?dāng)_中起著至關(guān)重要的作用�,必須在設(shè)計中予以考慮。

2.提出并驗證了幾種緩解方法�,例如:在設(shè)計和制造技術(shù)允許的范圍內(nèi)使用盡可能小的反焊盤;布線時使走線遠(yuǎn)離反焊盤以應(yīng)對層對位偏差�;對于高速引腳區(qū)域布線�,盡可能保持引出長度最短�。

參考文獻(xiàn)

[1]B. Chia, R. Kollipara, et al., “Study of PCB Trace Crosstalk in Backplane Connector Pin Field”, 2006 IEEE Electrical Performane of Electronic Packaging, Scottsdale, AZ, USA, 2006.

[2]J. Tang et al., "Far End Crosstalk Mitigation of Differential High Speed Interconnects Within Printed Circuit Board Via Fields," 2021 IEEE 30th Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), Austin, TX, USA, 2021.

[3]J. Tang, J. A. Hejase, P. RoyPaladhi, W. D. Beckir and D. M. Dreps, "A Comprehensive Signal Integrity Study of Differential Pairs Routed within a PCB Via Field," 2018 IEEE 27th Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), San Jose, CA, USA, 2018.

[4]X. Ye, A. Sutono, D. Liu, V. Gupta, “Extended Unterminated Line (EUL) for accurate and efficient crosstalk measurement”, IEEE international symposium on EMC, 2018.