指動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器(DRAM)在一段時(shí)間內(nèi)維持所存儲(chǔ)數(shù)據(jù)的能力,該能力受漏電�����、溫度和器件老化等因素影響��。

什么是 DRAM Retention�����?

DRAM 數(shù)據(jù)保持指的是 DRAM 存儲(chǔ)單元在無(wú)需刷新的情況下維持所存數(shù)據(jù)的能力�����。與靜態(tài)隨機(jī)存取存儲(chǔ)器(SRAM)不同��,DRAM 依靠電容來(lái)存儲(chǔ)每一位數(shù)據(jù)���,因此必須周期性地進(jìn)行刷新操作。隨著時(shí)間推移���,電容會(huì)逐漸漏電��,若未及時(shí)刷新�����,將導(dǎo)致數(shù)據(jù)丟失���。

影響 DRAM 數(shù)據(jù)保持的關(guān)鍵因素

漏電流:

DRAM 數(shù)據(jù)保持的主要挑戰(zhàn)在于電容中存儲(chǔ)的電荷會(huì)隨時(shí)間泄漏��。這種漏電受存儲(chǔ)單元結(jié)構(gòu)及其周邊電路設(shè)計(jì)的影響���。

溫度:

高溫會(huì)加速電荷泄漏,從而縮短數(shù)據(jù)保持時(shí)間�����。因此��,在高溫環(huán)境下���,DRAM 需要更頻繁地刷新以防止數(shù)據(jù)丟失��。

老化:

隨著 DRAM 芯片使用時(shí)間增長(zhǎng)��,其數(shù)據(jù)保持性能會(huì)逐漸退化�����。研究表明�����,芯片老化會(huì)導(dǎo)致保持錯(cuò)誤率上升�����,進(jìn)而引發(fā)性能下降甚至潛在的安全漏洞�����。

數(shù)據(jù)模式:

相鄰存儲(chǔ)單元中存儲(chǔ)的數(shù)據(jù)可能通過(guò)電耦合影響目標(biāo)單元的保持時(shí)間。某些特定的數(shù)據(jù)排列會(huì)產(chǎn)生噪聲�����,干擾存儲(chǔ)電荷的穩(wěn)定性���,造成保持時(shí)間波動(dòng)。

漏電機(jī)理

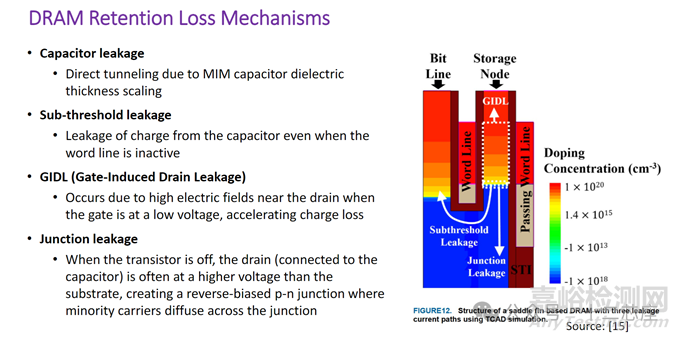

直接隧穿:

由于金屬-絕緣體-金屬(MIM)電容的介質(zhì)層厚度不斷微縮�����,導(dǎo)致電子通過(guò)量子隧穿效應(yīng)直接穿過(guò)介質(zhì)層。

亞閾值漏電:

即使字線(WL)處于非激活狀態(tài)�����,電容中的電荷仍會(huì)通過(guò) MOSFET channel 發(fā)生泄漏。

柵極誘導(dǎo)漏極泄漏(GIDL):

當(dāng)柵極處于低電壓時(shí)��,漏極附近因高電場(chǎng)作用而產(chǎn)生帶電載流子���,加速電荷流失��。

結(jié)漏電(Junction Leakage):

當(dāng)晶體管關(guān)斷時(shí)��,與電容相連的漏極通常處于比襯底更高的電位��,形成反向偏置的p-n結(jié)�����,此時(shí)少數(shù)載流子會(huì)擴(kuò)散穿過(guò)該結(jié),造成電荷泄漏���。

Reference:

1.DRAM and NAND Reliability in AI era.

2.2025 FMS.